CFET to complete the nanosheet family in the logic technology roadmap

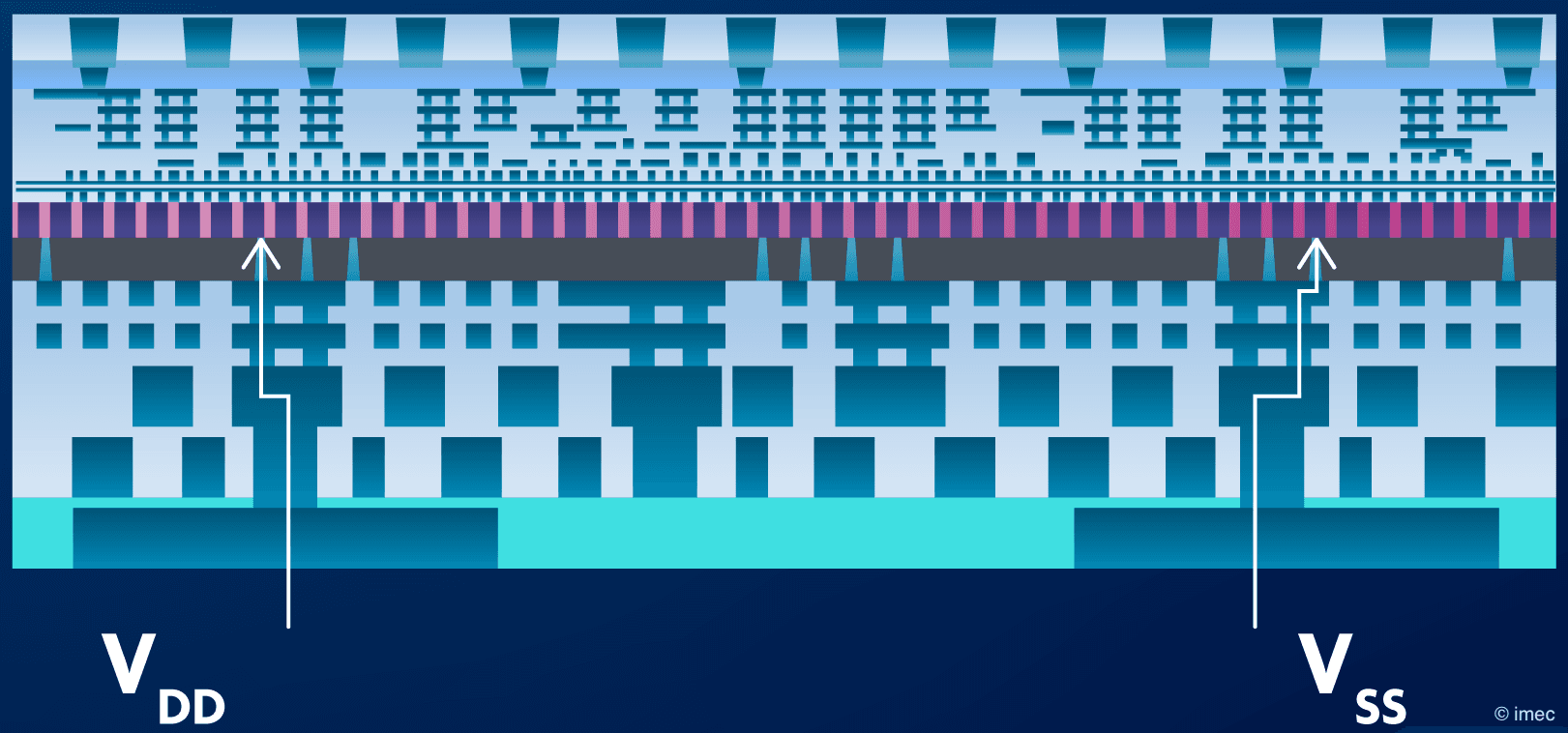

Hans Mertens, principal member of technical staff at imec: “Today, the semiconductor industry is in a transition period from FinFET to Nanosheet, a device architecture that will extend the roadmap with multiple logic technology generations. Along the road, we might introduce the Forksheet, an advanced nanosheet architecture that we proposed a few years ago, with reduced separation between adjacent devices, offering both scaling and performance advantages compared to conventional nanosheet. Towards the end of the decade, we expect the complementary FET (CFET) to enter the roadmap. In this device architecture, n- and pMOS devices are stacked on top of each other, removing for the first time the n-p separation from standard cell height considerations. When complemented with advanced technologies to contact the transistors, CFET will allow to gradually push track heights from 5T to 4T and even beyond, effectively shrinking standard cell size substantially.

From processing point of view, CFET fabrication is challenging due to the nMOS-pMOS vertically stacked structure, and we are in the early stages of pathfinding. Several flavors of CFETs have been proposed, including monolithic and sequential process flows. In a sequential process flow, top-tier devices are processed sequentially after transfer of a blanket semiconductor layer by wafer bonding on top of bottom-tier devices. Monolithic integration, on the contrary, involves building the vertical device architecture on a single substrate.”

Monolithic CFET: the fastest path to CFET introduction

Anne Vandooren, principal member of technical staff at imec: “Within our logic program, imec and its partners focus on monolithic CFET integration, as this integration scheme is the least disruptive compared to existing nanosheet-type process flows. It is therefore believed to offer the fastest path to CFET introduction at industry-relevant dimensions. Nevertheless, the vertical stacking of layers from which both devices will be fabricated drives a need for high-aspect ratio patterning, selective deposition and removal of materials, and the deposition of high-quality (epi-)films. In addition, some CFET-specific process modules will need to be introduced to enable vertical isolation in the gate and contact part of the cross-section.

We address these challenges by partitioning the monolithic CFET integration challenge into different sub-projects, with gradually increasing integration complexity. Each sub-project builds on a different test vehicle. We first focus on unipolar monolithic CFET, with n and p top and bottom devices processed on different wafers. The other test vehicles will have monolithic CMOS CFET devices processed on the same wafer. They mainly differ in the way the CFET devices are contacted, eventually working towards advanced middle-of-line (MOL) and backside connectivity options. For each of the test vehicles, we explore various process and integration options, trading off power-performance-area gains against complexity. The learnings obtained on each of the vehicles is transferred to the next.”

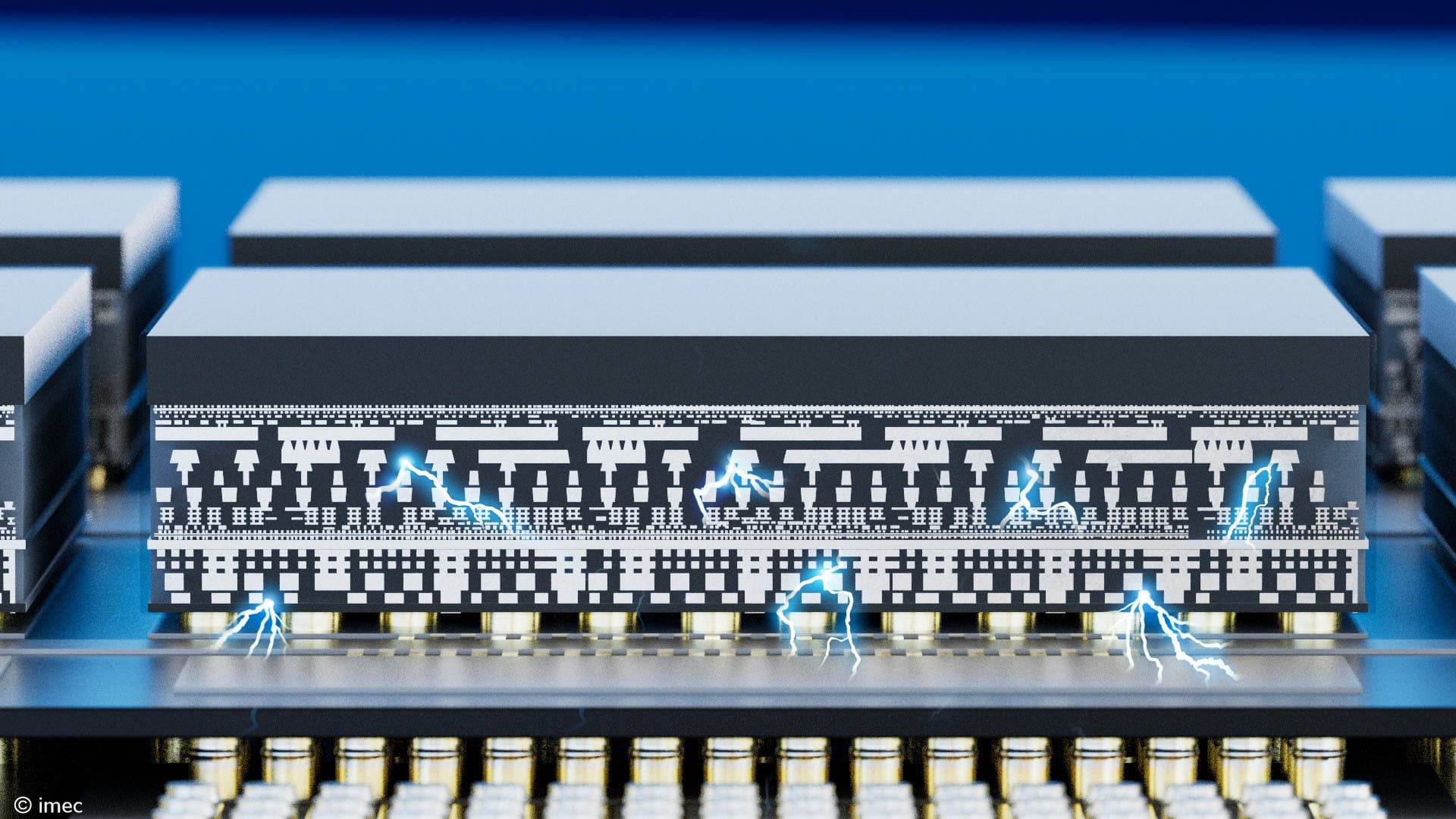

Unipolar monolithic CFET demonstration at 48nm gate pitch

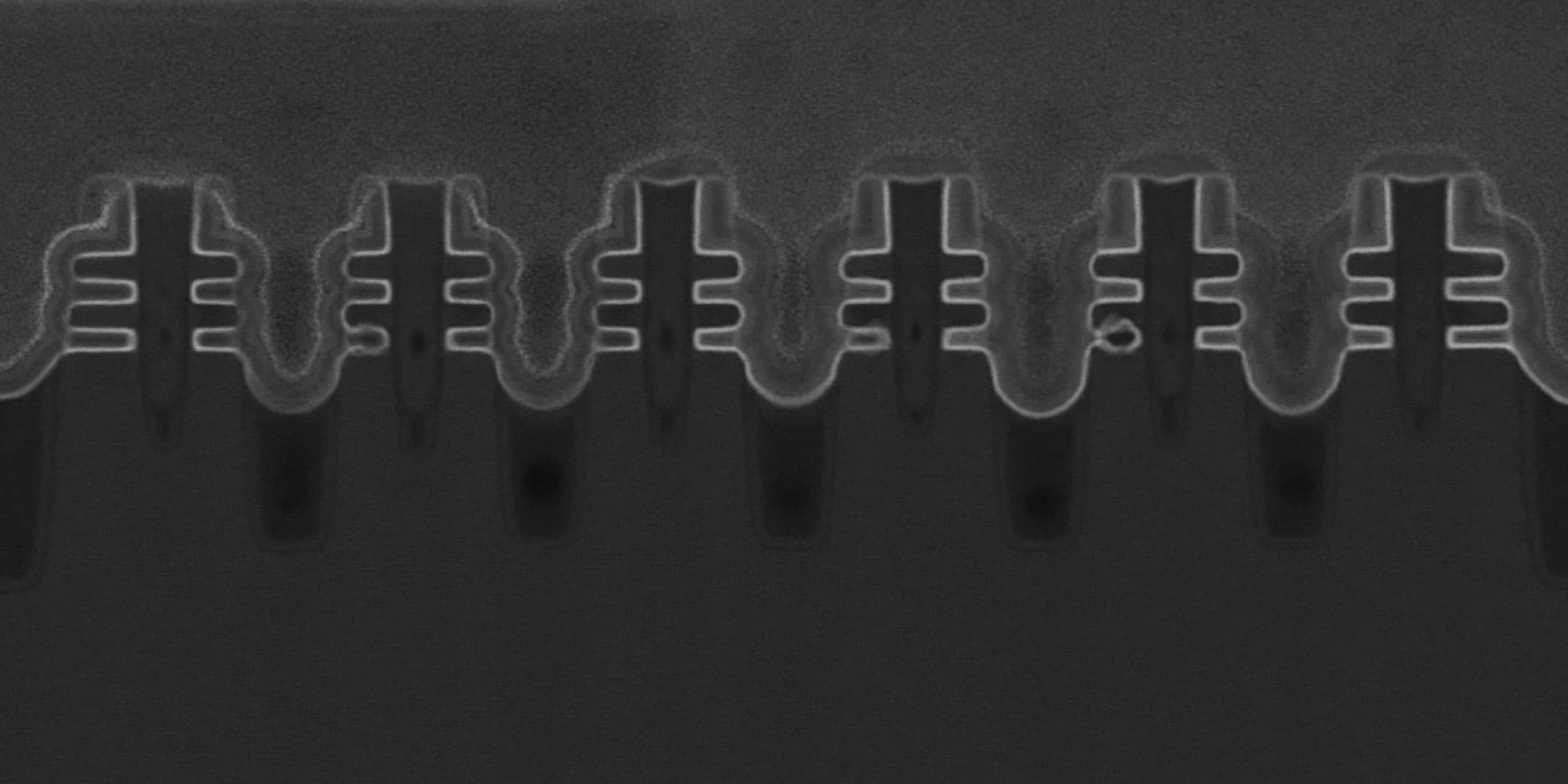

Hans Mertens: “At VLSI 2020, imec was the first to demonstrate monolithic CFET devices on a 300mm wafer, although at a ‘relaxed’ gate pitch (i.e., contacted poly pitch (CPP)) of 90nm. At VLSI 2023, imec presented unipolar CFET devices built through monolithic integration at industry-relevant 48nm gate pitch [1]. This work was selected for the 2023 VLSI Technology Symposium Highlights session. Our functional devices showed excellent switching characteristics for bottom and top devices separately, for both n- and pMOS. We are currently exploring unipolar monolithic CFET integration at even smaller gate pitch.

End-of-process cross sectional images for (a) bottom pFET and (b) top nFET (LG,PHYS=27nm) (as presented at VLSI 2023).

In this demonstration, the source-drain epitaxial structures (source-drain epi) and source-drain contacts are evaluated for either bottom or top devices. In addition, to limit the aspect ratio and be faster in the development, the active part of the structure was limited to only one nanosheet for the bottom and one for the top device. The significance of this work, however, is to show that, with a vertical separation of only 30nm between top and bottom sheets, we found a way to independently contact top and bottom devices. It is a steppingstone for advanced CFET integration at scaled dimensions.”

Monolithic CMOS CFET: challenging process steps and modules

Steven Demuynck, scientific director at imec: “In addition, we continue our efforts to enable monolithic CMOS CFET device demonstration, a project strategic to imec, enabled by intense collaboration with our partners. Unlike for the unipolar CFET devices, stacked p-bottom and n-top devices will now be implemented on the same wafer and contacted independently. In addition, the integration flow should allow differentiating the threshold voltage (Vt) setting on the two devices that share a common gate – all at an industry relevant gate pitch of 50nm. This vertical architecture has major implications. It requires not only the development of three new, CFET-specific process modules, but also adjustments to the other modules in the process flow to accommodate the presence of these CFET-specific modules.

A first CFET-specific process module, which we refer to as the middle dielectric isolation (MDI), stems from the need to create a vertical dielectric isolation between top and bottom gate to differentiate on the Vt setting between top and bottom devices. To enable this, our team proposed a unique solution that affects the process flow from the start: the Si/SiGe stack, formed to create the active part of the CFET, is turned into a taller Si/SiGe1/SiGe2 multilayer stack, with higher Ge% for SiGe2 than for SiGe1. While sacrificial SiGe1 layers are replaced with the work function metals setting the Vt, the Ge-rich sacrificial layers are converted into the MDI dielectric creating the n-p WF metal separation within the gate. The stack allows for the formation of an inner spacer on the Ge-deficient layer in the stack – a critical nanosheet-specific feature that isolates the gate from the source-drain. Finding the most efficient way to co-integrate the bottom source-drain, the new MDI module and inner spacer at this tight pitch and for high aspect ratio geometries is currently the focus of our R&D effort.

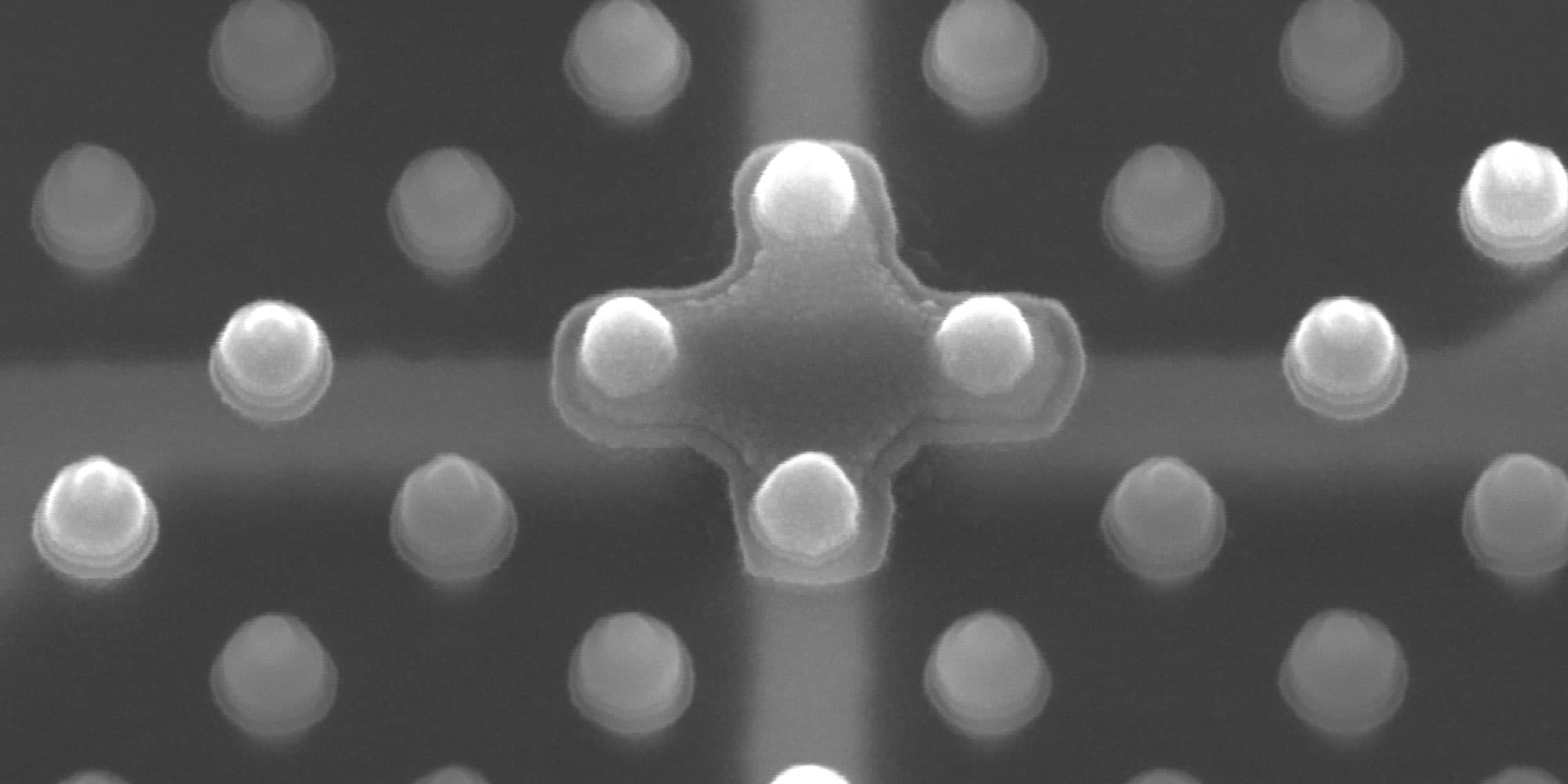

A second vertical isolation is needed between the source-drain contact metals of the top and bottom devices. Various options are explored to build and isolate bottom and top contacts – deep in between two tall gates – and subsequently route bottom and top transistors. A morphological proof of concept flow demonstrating the capability to fabricate a stacked MOL was shared at VLSI 2023 [2].

And finally, we need to encapsulate the top channel when growing the source-drain epi on the bottom device. This will effectively enable growing differentially doped epi on bottom and top devices.”

Connecting the CFET devices from the backside

Anne Vandooren: “On the longer term, we are exploring advanced integration options to connect the active devices from the backside. The developments are driven by the need to further reduce standard cell heights and avoid routing congestion in the back-end-of-line at the frontside of the wafer.

Backside contacting introduces additional process steps, including wafer bonding and substrate thinning from the backside. These steps challenge a very tight overlay for aligning the backside layers to the small features already present in the frontside. This is even more challenging as wafer deformation occurs during bonding, requiring the use of specific litho overlay correction methods. In addition, an extra process module is needed to provide proper isolation between the backside metal 1 and the active nanosheet part of the CFET device.”

CFET enablement: an industrial collaboration effort

Steven Demuynck: “Since we started CFET development, we have been seeing an increase in the intensity of engagement with our equipment suppliers. On the one hand, these vendors want to be involved in a very early stage of development to be able to identify where their tools, processes, and materials may fit into this roadmap. They also want to understand the context in which these would need to operate, to create awareness of interactions up- and downstream in the flow. Imec plays a pivotal role in supplying these companies with wafers that have CFET-relevant topologies and geometries. Such material is usually not readily available to them before development begins at IDMs. On the other hand, these collaborations bring benefits for imec as well. The collaboration with our tool vendors helps us tap into the most advanced capabilities of our partners.

In parallel, our logic core partners take an interest in identifying the key challenges and potential roadblocks that we encounter by evaluating various flow flavors. Understanding at an early stage what hardware and processes are enabling, can give them a head start in embarking on a R&D effort on their part.”

Want to know more?

[1] ‘Nanosheet-based complementary field-effect transistors (CFETs) at 48nm gate pitch, and middle dielectric isolation to enable CFET inner spacer formation and multi-Vt patterning’, H. Mertens et al., VLSI 2023;

[2] ‘Integration of a stacked contact MOL for monolithic CFET’, V. Vega-Gonzalez et al., VLSI 2023.

Interested in receiving these papers? Fill in our contact form.

Steven Demuynck received a M.S degree in physics from K.U. Leuven (1994) and a Ph.D. degree in physics from KU Leuven, Belgium, in 2000. He joined imec in 2001, where he is currently scientific director. In this role, he is driving the integration effort aimed at demonstrating functional CMOS monolithic CFET.

Anne Vandooren received her M.S. degree in electrical engineering from the Université Catholique de Louvain (UCL) in Belgium in 1996, and her Ph.D. degree in electrical engineering from the University of California, Davis in 2000. From 2000 to 2007, she was a senior researcher at Motorola/Freescale working on the integration of FDSOI and FinFET technologies. She joined imec in 2007, where she is principal member of technical staff. In this role, she focuses on the development of novel CFET architectures including monolithic and sequential approaches as well as backside connection.

Hans Mertens received a M.S. degree in applied physics from Eindhoven University of Technology (2002) and a Ph.D. degree in physics from Utrecht University (2007), both in The Netherlands. From 2007 to 2012 he was a senior scientist at NXP Semiconductors, working on SiGe heterojunction bipolar transistors for RF applications. He joined imec in 2012, where he is a principal member of technical staff. In this role, he focuses on exploring novel integration solutions for advanced CMOS transistor architectures, including CFETs.

Published on:

19 June 2023