CFETs entering the logic technology scaling roadmap

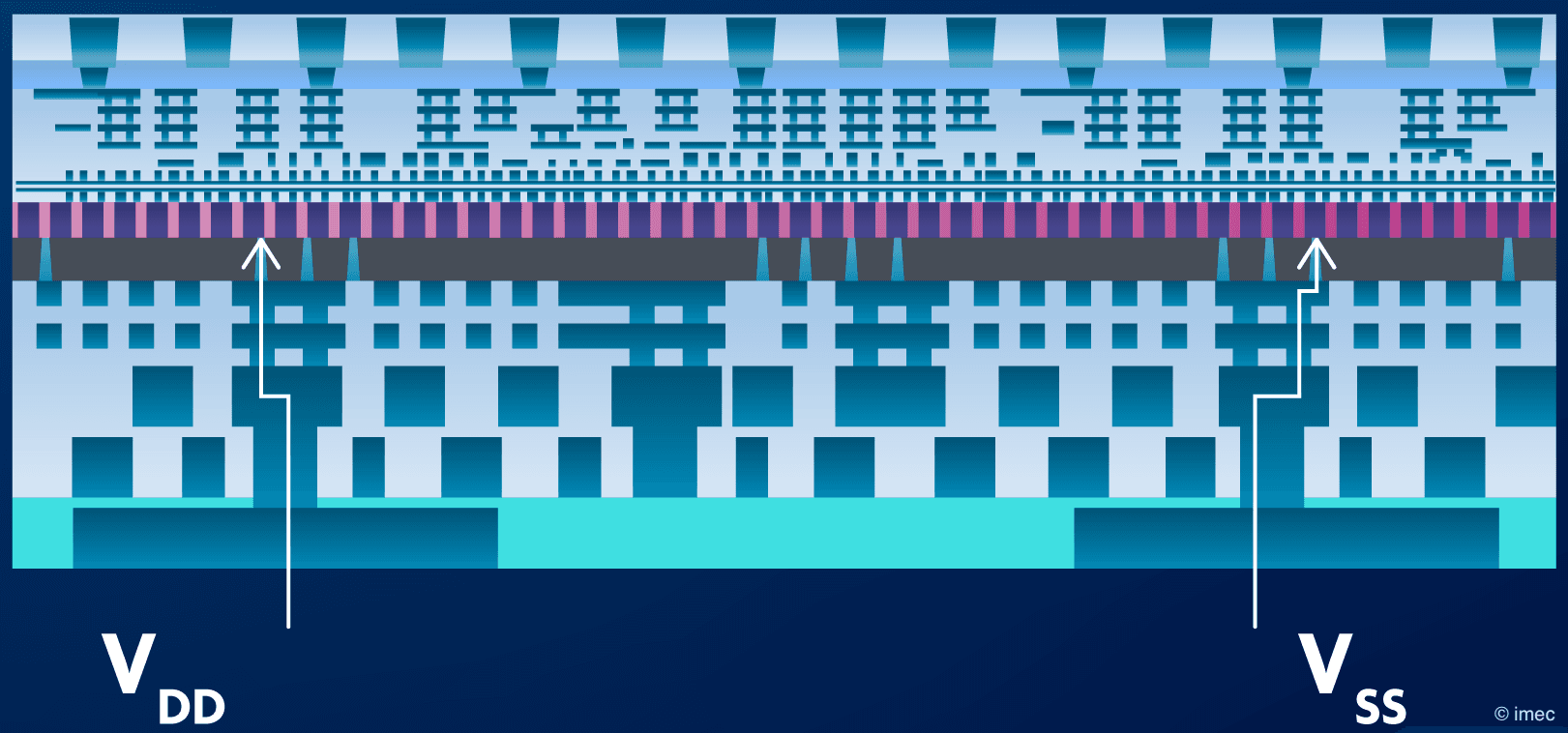

At VLSI 2021, imec introduced the forksheet device architecture to extend the scalability of the nanosheet transistor family towards 1nm and beyond logic nodes. In a forksheet device, the effective channel widths can be made larger than in a conventional gate-all-around nanosheet device due to a reduced spacing between n- and p-type transistors. This benefits the transistor’s drive current (or DC performance). In addition, the smaller n-to-p spacing enables a further reduction of the standard cell height. This gradually pushes standard cells towards 4T track height design. And means that 4 intracell metal lines fit in the range of the standard cell height.

But for 4T cell designs and metal pitches as tight as 16nm, even the forksheet becomes too narrow and struggles to deliver the required performance. This challenge is highlighted in the 2022 VLSI paper by P. Schuddinck et al. [1]. And that’s where the complementary FET or CFET can provide relief.

In a CFET architecture, n- and pMOS devices are stacked on top of each other, allowing further maximization of the effective channel width.

Julien Ryckaert: “In a CFET architecture, n- and pMOS devices are stacked on top of each other. Stacking removes the n-p spacing from cell height considerations. This allows further maximization of the effective channel width, and, hence, the drive current. We can also use the resulting area gain to push track heights to 4T and below.”

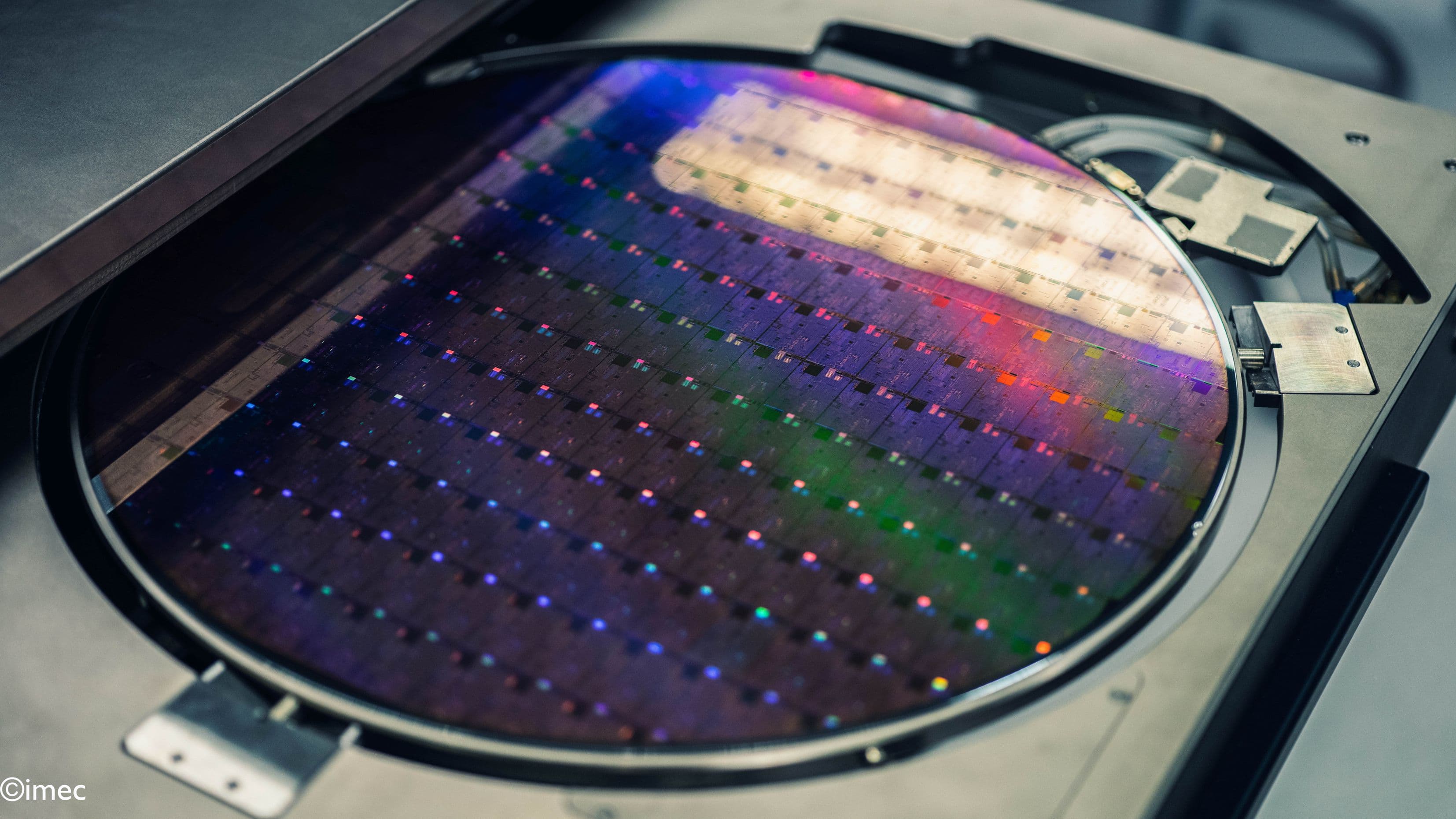

Figure 1 - From FinFET to nanosheet to forksheet and finally to CFET.

Do you want regular updates on imec’s semiconductor research?

Two CFET implementation schemes: monolithic and sequential

Two possible integration schemes are being explored for enabling the challenging nMOS-pMOS vertical stacking: monolithic versus sequential.

A monolithic CFET flow starts with the epitaxial growth of the bottom channel. That is followed by the deposition of an intermediate sacrificial layer. Next comes the epitaxial growth of the top channel. Naoto Horiguchi: “Although this seems the most straightforward way to build CFETs, the processing flow is rather complex. For example, the stacking approach results in very high-aspect-ratio vertical structures. This brings critical challenges for further patterning the fin, gate, spacers, and source/drain contacts.”

Imec develops modules and integration steps, and quantifies the power-performance-area-cost (PPAC) benefits and the complexity of monolithic and sequential process flows.

Update: towards a process flow for monolithic CFET transistor architectures

Alternatively, CFETs can be made using a sequential fabrication flow consisting of several blocks. First, the bottom tier device is processed up to the contacts. Next, a blanket semiconductor layer is created on top of this tier by wafer transfer, using a wafer-to-wafer bonding technique. Then, the top-tier device is integrated, and the top and bottom gates are connected. Julien Ryckaert: “From an integration point of view, this flow is simpler than the monolithic flow, as both bottom- and top-tier devices can be processed separately in a conventional ‘two-dimensional’ way. In addition, it offers the unique possibility of integrating different channel materials for n- and p-type devices.”

Each of these flows comes with its own set of pros and cons. Imec contributes by developing modules and integration steps. And by quantifying the power-performance-area-cost (PPAC) benefits and the complexity of each process flow.

PPAC benchmark: (optimized) sequential CFET is a valid alternative to monolithic CFET

In the 2022 VLSI paper by P. Schuddinck et al., the authors present a PPAC evaluation of monolithic CFET vs. sequential CFET in a 4T standard cell design [1].

Julien Ryckaert: “From this benchmark, CFETs fabricated using a monolithic process flow are shown to consume less area and outperform their sequential counterparts, which suffer from a rise in effective capacitance. However, we show that we can put the trajectory of the sequential CFET on par with that of monolithic CFETs by applying three optimizations: (1) self-aligned gate merge ((v2) in the figure), (2) omission of the gate cap (v3), and (3) the use of hybrid orientation technology, referred to as HOT.”

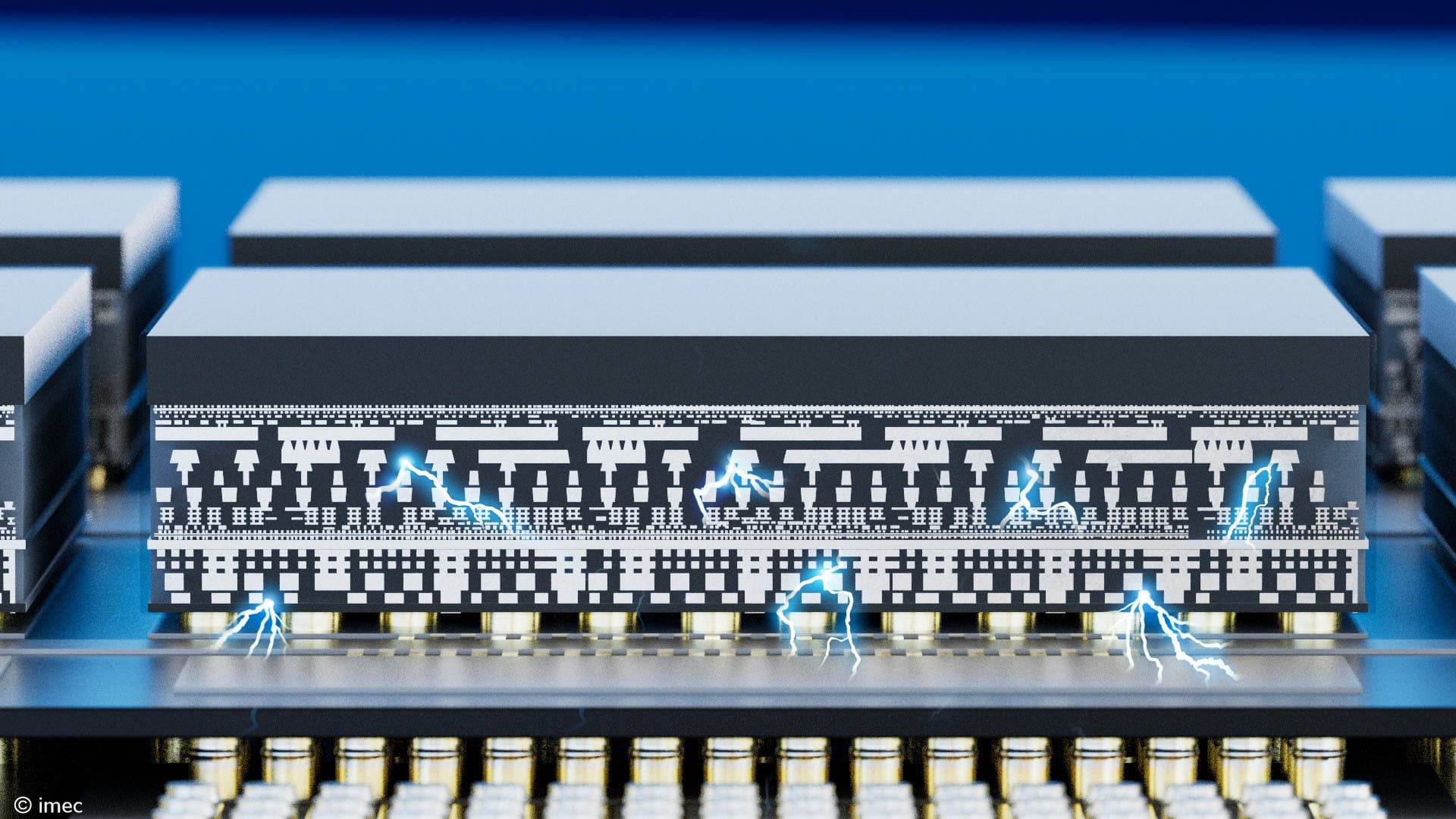

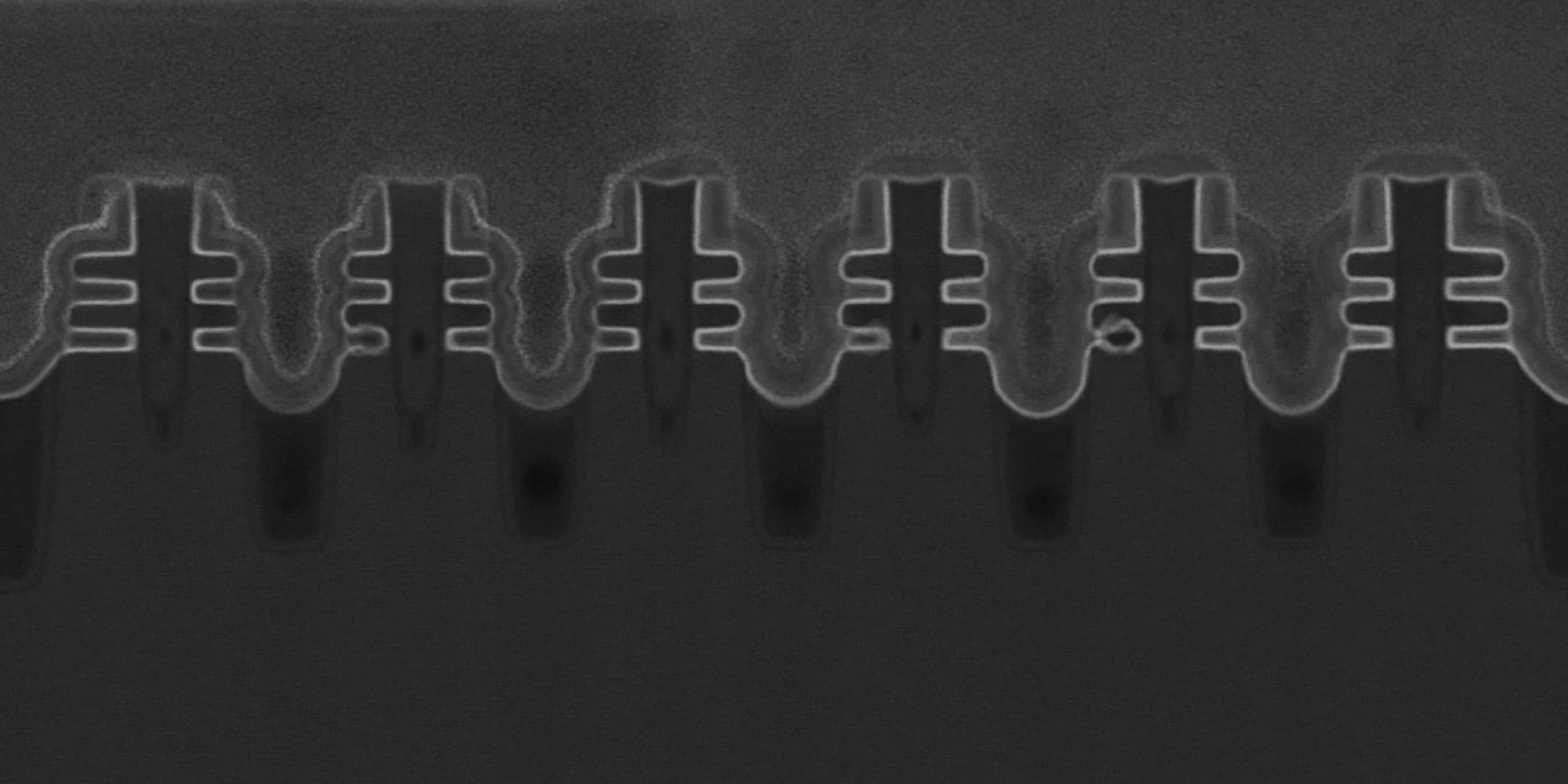

Figure 2 – Gate cross sections for nansoheet (NS), forksheet (FS) and CFET (monolithic and sequential). Basic sequential CFET (=v1) is wider and taller than mono. With an optimized flow (including self-aligned gate merge (v2) and no gate cap (v3)), sequential CFET approaches monolithic CFET in terms of area consumption (also presented at VLSI 2022).

HOT allows for independently optimizing the crystal orientation and strain engineering of top and bottom devices without adding to the process flow cost. For example, in an n-on-p configuration, Si wafers with <100> orientation can be used on top, delivering the highest electron mobility for the top nMOS devices. While for the bottom, pMOS hole mobility benefits from the <110> Si wafer orientation. Julien Ryckaert: “Although monolithic CFET remains the preferred choice, the uniqueness of the sequential process flow is that it can exploit this difference in wafer orientation.

Although monolithic CFET remains the preferred choice, the uniqueness of the sequential process flow is that it can exploit a difference in wafer orientation for bottom and top-tier devices.

With these optimizations, our benchmark shows that the sequential CFET flow can be a valid alternative to the more complex monolithic CFET for future 4T track designs.”

Gradual improvement in module and integrations steps

In recent years, imec reported incremental progress in improving module and integration steps for monolithic and sequential CFETs.

At VLSI 2020, for example, imec was the first to demonstrate a monolithically integrated CFET architecture realized by optimizing critical module steps [2].

For sequential CFET, step-by-step improvements have been reported as well. Bottom and top-tier devices can be processed separately in a conventional ‘two-dimensional’ way. But the wafer transfer brings specific challenges. For example, it comes with thermal budget constraints (to around 500°C or below) for both layer transfer and top-tier device processing to avoid any negative impact on the bottom-tier devices. This is a concern for the gate-stack reliability of the top-tier device, which usually requires thermal steps of the order of 900°C. Earlier, imec demonstrated new approaches for maintaining good gate-stack reliability. These include, among others, a low-temperature hydrogen plasma treatment for pMOS top devices [3]. Also, imec reported progress in the dielectric-to-dielectric wafer bonding step by developing a void-free thin bonding oxide process.

An optimized low-temperature Smart CutTM layer transfer process – the critical building block for sequential CFET

In the 2022 VLSI paper by A. Vandooren and al., imec evaluated three different processes for enabling layer transfer [4]. In this paper, the authors studied the impact of the various process options on the device performance for both top (fully depleted silicon-on-insulator (FD-SOI)) and bottom (bulk FinFET) devices.

Naoto Horiguchi: “Especially promising from a cost perspective is SOITEC’s low-temperature Smart CutTM flow. This uses an engineered bulk donor wafer to enable thin layer splitting at low temperature. The beauty of this approach is that it allows for reusing the donor wafer, making it a cost-effective solution. The other two approaches both rely on substrate removal by grinding and Si etch-back, which does not allow reuse of the donor wafer.”

Figure 3 – Description of the SOITEC low-temperature Smart CutTM layer transfer flow, with no curing or low-temperature curing (also presented at 2022 VLSI).

With further optimization, the top-tier devices processed after proof-of-concept layer transfer with low-temperature Smart CutTM are shown to recover from degraded electrical performance. Naoto Horiguchi: “The devices suffer from lower electron mobility due to the non-optimized low-temperature curing. Soitec has further developed its solution. It showed that we can recover the mobility loss by optimizing the low-temperature curing step, which improves the crystal quality of the Si channel. Given the cost-effectiveness of this approach, we consider Smart CutTM with the newly developed process conditions a valid option for performing layer transfer in sequential CFET process flows.

SOITEC's low-temperature Smart CutTM flow with newly developed process conditions is a valid option for performing layer transfer in sequential CFET process flows.

It provides a generic flow enabling 3D sequential stacking applications beyond CFET, such as 3D sequential integration of memory-on-logic or logic-on-logic.”

Figure 4 – Electron effective field mobility vs. inversion charge for the low-temperature Smart CutTM layer transfer approach, comparing optimized and reference (proof-of-concept) process conditions. The graph shows improved mobility for Opt. B (purple), which refers to the additional low-temperature curing step (also presented at VLSI 2022).

With these test devices, the authors also showed good electrical interconnectivity between the top and bottom devices, validated through functional inverter chains. In addition, gate stack reliability of the top-tier pMOS devices was preserved by integrating the hydrogen plasma treatment step, as discussed above.

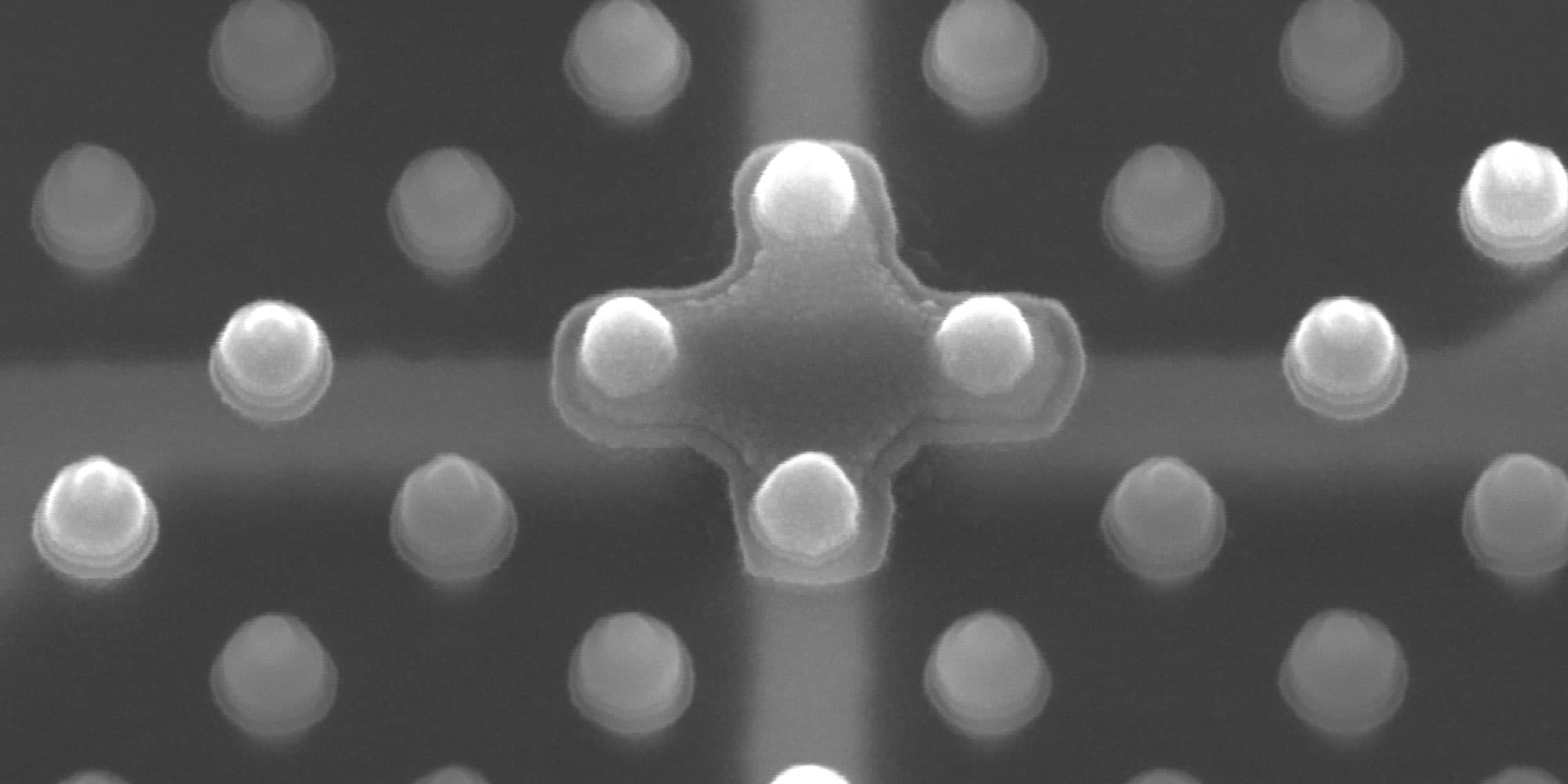

Figure 5 – TEM cross-section of the 3D sequentially stacked devices (also presented at VLSI 2022).

“I want to emphasize that this architecture is not yet a true CFET implementation,” adds Naoto Horiguchi. “For example, in the envisioned sequential CFET architecture, the metal interconnect layer (M1B) for the bottom device is absent. Our test vehicle, shown in the VLSI paper by A. Vandooren, was used to demonstrate improved layer transfer as a key module for sequential CFET and other 3D sequential stacking implementations. In the future, we continue to work towards optimized integration steps, which will eventually demonstrate a true sequential CFET implementation.”

Want to know more?

Imec’s work on CFET PPAC evaluation and low-temperature Smart CutTM is described in the following 2022 VLSI papers. Interested in receiving the papers? Fill in our contact form.

[1] ‘PPAC of sheet-based CFET configurations for 4 track design with 16nm metal pitch’, P. Schuddinck et al., 2022 VLSI;

[4] ‘Demonstration of 3D sequential FD-SOI on CMOS FinFET stacking featuring low temperature Si layer transfer and top tier device fabrication with tier interconnections’, A. Vandooren et al., 2022 VLSI;

Further reading:

- [2] ‘First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers’, S. Subramanian et al, VLSI 2020;

- [3] ‘Atomic Hydrogen Exposure to Enable High-Quality Low-Temperature SiO2 with Excellent pMOS NBTI Reliability Compatible with 3D Sequential Tier Stacking’, J. Franco et al, IEDM 2020;

- ‘Imec presents forksheet device as the ultimate solution to push scaling towards the 2nm technology node’, imec press release;

- ‘Entering the nanosheet transistor era’, imec reading room;

- ‘Logic technology scaling options for 2nm and beyond’, imec reading room.

Naoto Horiguchi is the Director of CMOS Device Technology at imec. He obtained a degree in Applied Physics in 1992 from the Tokyo University, Japan. He has worked in Fujitsu and the University of California Santa Barbara, where he was involved in developing devices using semiconductor nanostructures and advanced CMOS. He has been with imec since 2006, where he is engaged in advanced CMOS device R&D together with worldwide industrial partners, universities, and research institutes. His current focus is on CMOS device scaling down to the 1nm technology node and beyond.

Julien Ryckaert received an M.Sc. degree in electrical engineering from the University of Brussels (ULB), Belgium, in 2000 and a Ph.D. degree from the Vrije Universiteit Brussel (VUB) in 2007. He joined imec as a mixed-signal designer in 2000, specializing in RF transceivers, ultra-low power circuit techniques, and analog-to-digital converters. In 2010, he joined the process technology division in charge of design enablement for 3DIC technology. Since 2013, he oversees imec’s design-technology co-optimization (DTCO) platform for advanced CMOS technology nodes. In 2018, he became program director focusing on scaling beyond the 3nm technology.

Published on:

16 June 2022