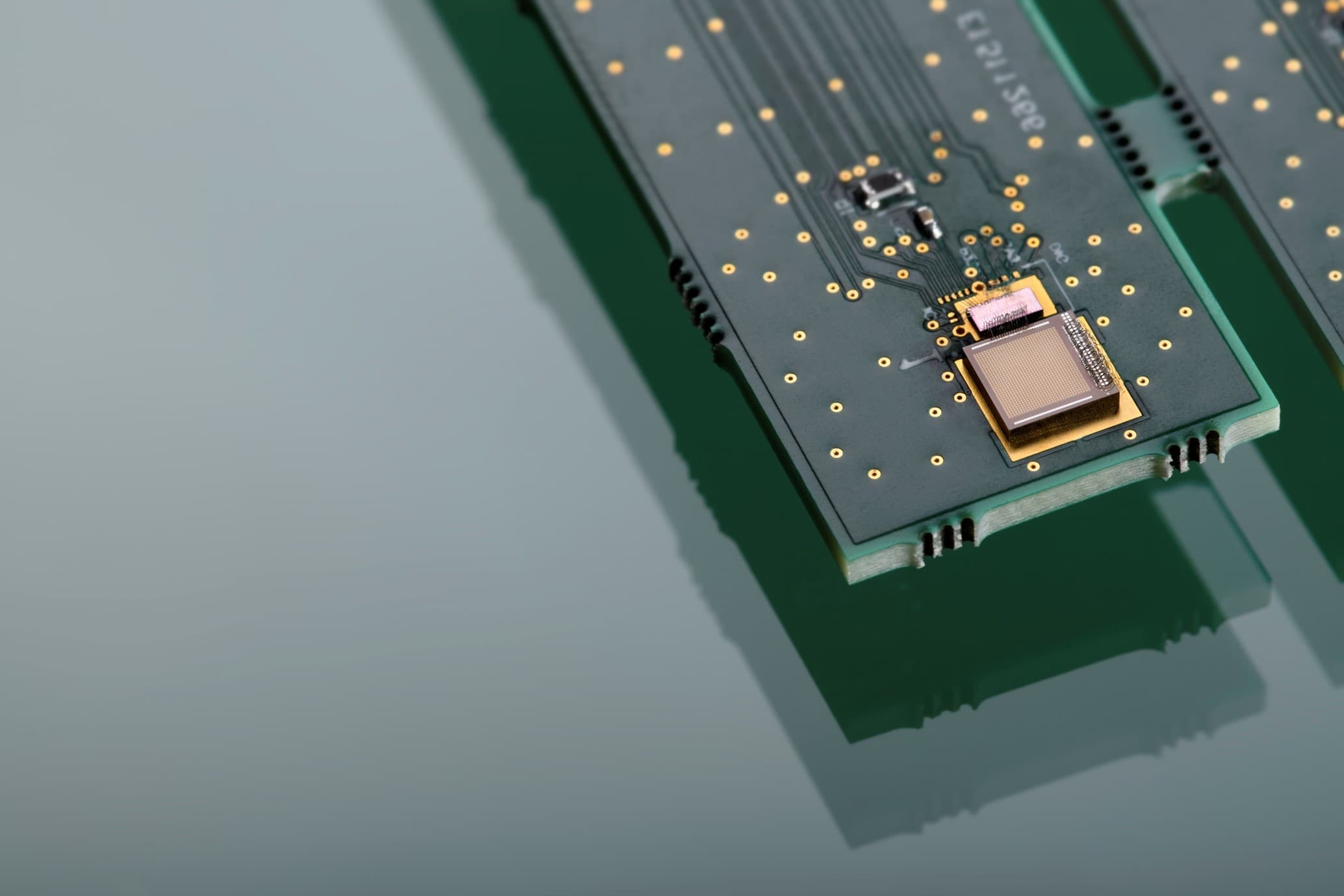

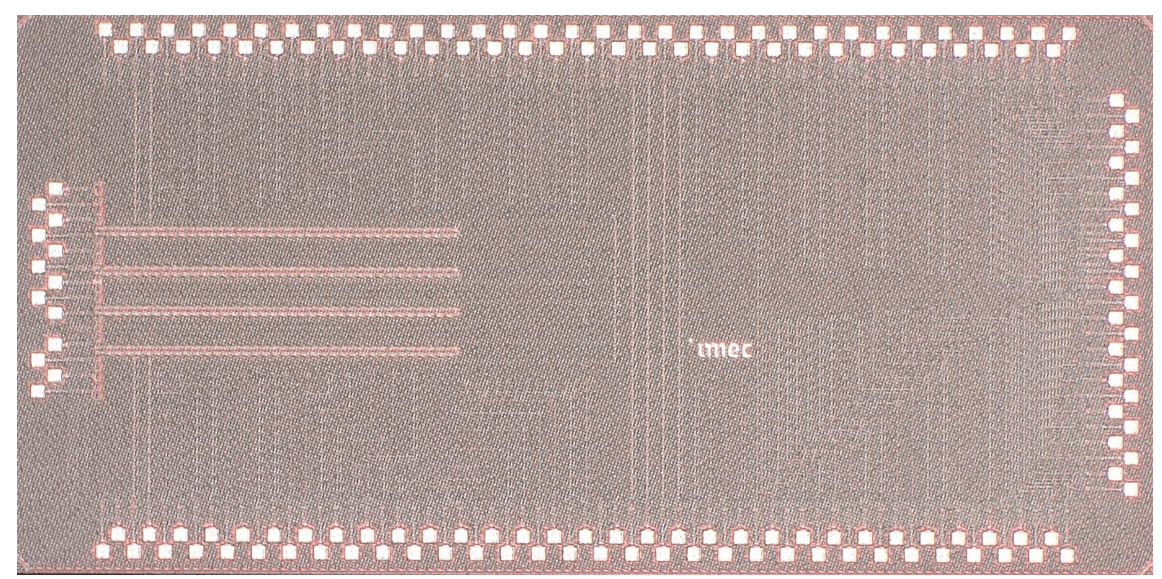

Next-generation brain implants aim to be smaller and carry more electrodes while consuming low power. Imec recently designed a new low-power, miniature chip for large-scale recordings that is 16 times smaller than the state of the art. The impressive miniaturization (total area per channel of 0.005 mm2) was achieved by applying smart design solutions on the one hand and harnessing the advantages of a smaller technology node on the other hand. The chip uses a direct digitization architecture which aims at converting the weak neural signals from the analog to the digital domain as close as possible to the electrodes that capture them. This approach saves area and improves the signal quality. In addition, with this new prototype, the team explored for the first time a 22nm CMOS technology.

At the same time, imec is working on the wireless transfer of the enormous amounts of data these high-density probes create. They designed an ultra-wideband (UWB) transmitter chip that pushes data rates up to 1.66 Gb/s using little power. In addition, the researchers increased the wireless part of the system by removing the wire between the implant and the head-mounted or subcutaneous module. Using galvanic-coupled body channel communication, imec demonstrates a transdural link that can transmit the implant’s data at an incredible >250 Mbps data rate. Lastly, the team works on ways to compress the data. A clever neuromorphic sensing system based on how neurons relay information demonstrates data compression rates of >125 times, barely requiring energy. These advancements will enable the next leap into miniature, high-density, low-power wireless brain implants.

Read all the details in the full article, published in DesignNews

Yao-Hong Liu is currently Scientific Director in imec. He is a recipient of European Research Council (ERC) Consolidator grant. He is also a guest professor at Delft University of Technology. His current research focuses on wireless communication and edge computation for implantable brain-computer interfaces (BCIs) and IoT applications.Dr. Liu received his Ph.D. degree from National Taiwan University, Taiwan, in 2009. He was with Terax, Via Telecom (now Intel), and Mobile Devices, Taiwan, from 2002 to 2010, developing wireless transceiver ICs. Since 2010, he joined imec, the Netherlands, and is leading the research of the ultra-low power ASIC design. He received the IEEE Brain and Solid-State Circuits joint-society best paper award honorable mention 2022. He is currently a steering committee member of IEEE RFIC symposium.

Carolina Mora Lopez received the Ph.D. degree in electrical engineering from KU Leuven, Leuven, Belgium, in 2012, in collaboration with imec, Leuven. From 2012 to 2018, she worked as a Researcher and an Analog Designer with imec focused on interfaces for neural-sensing applications. She is currently the Scientific Director and the Team Leader of the circuits for neural interfaces team with imec. Her research interests include analog and mixed-signal circuit design for sensors, bioelectronics, and neural interfaces. Dr. Mora Lopez is an IEEE SSCS Distinguish Lecturer and serves on the Technical Program Committee of the VLSI Circuits Symposium, International Solid-State Circuits Conference (ISSCC), and ESSCIRC conferences.

Published on:

26 October 2023