Ultimate Nano-interconnects: Pioneering Resilient Electronics

PhD - Leuven | More than two weeks ago

Background:

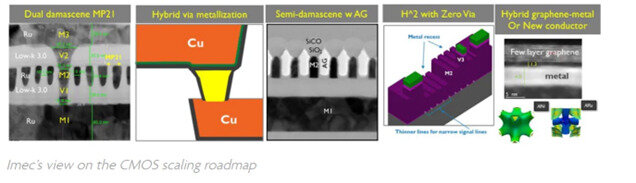

Nano-interconnects, with their unique mechanical, electrical, and thermal properties, are critical components of next-generation chips and flexible electronic systems. In addition to Cu as the backbone of interconnect technology, new metallization options for advanced chips including Ru, Mo, and their hybrids with graphene with <10 nm thickness are envisioned for use in advanced technology nodes and need to withstand extreme mechanical stresses and temperatures during chip-manufacturing and packaging. In addition, they will be exposed to harsh operational conditions in reliability-sensitive applications such as automotive.

The mechanical properties of nanowires often differ significantly from their bulk counterparts due to their small size and high surface-to-volume ratio which necessitates exploring how these size effects influence properties like elasticity, plasticity, and strength under various loading conditions. Understanding how nanowires deform under various stresses is crucial. This includes studying phenomena such as dislocation dynamics, phase transformations, and twinning. Nanowires can sustain much higher elastic strains compared to bulk materials. This property can be leveraged to tune electronic, optical, and thermal properties of nanowires through elastic strain engineering. On the other hand, the surface and interfacial properties of nanowires, such as surface and grain boundary energies and diffusivities play a significant role in their resilience and reliability.

Problem Statement:

A comprehensive understanding of thermo-mechano-diffusive properties, especially under various stress conditions and at sub 10 nm length-scale, remains elusive, posing a significant challenge for the development of next-generation semiconductor devices in terms of integrity and reliability. There is a need for advanced multi-scale modelling and characterization approaches to understand and predict these properties and ensure the reliability of the interconnects under various operational conditions.

Objectives:

The primary objectives of this research are:

- Objective 1: Develop and integrate multi-scale modelling approaches to study the thermo-mechano-diffusive properties of sub-10 nm interconnects. These include bridging molecular dynamics, kinetic Monte Carlo and finite element models.

- Objective 2: validate and corroborate models with experimental data. Including with in-situ testing approaches such as pico-indenter and nanoelectromechanical systems.

- Objective 3: leverage the predictive and validated models towards manufacturability and reliability of next generation technology nodes.

Related reading:

[1] https://www.imec-int.com/en/expertise/cmos-advanced/compute/beol

[2] H. Ceric, H. Zahedmanesh et al.. Electromigration-induced void evolution and failure of Cu/SiCN hybrid bonds, J. Appl. Phys. 133, 105101 (2023).

[3] A. S. Saleh, K. Croes, H. Ceric, I. De Wolf, H. Zahedmanesh, A framework for combined simulations of electromigration induced stress evolution, void nucleation, and its dynamics: Application to nano-interconnect reliability, J. Appl. Phys. 134, 135102 (2023).

[4] H. Zahedmanesh 2024, Electromigration in Nano-Interconnects: Determining Reliability Margins in Redundant Mesh Networks Using a Scalable Physical–Statistical Hybrid Paradigm, Micromachines 2024, 15(8), 956; https://doi.org/10.3390/mi15080956.

Required background: engineering science, engineering technology, computer science or equivalent

Type of work: 10% literature review, 60% numerical modelling. 30% experimental characterization

Supervisor: Houman Zahedmanesh

Co-supervisor: Michel Houssa

Daily advisor: Houman Zahedmanesh, Geoffrey Pourtois, Kris Vanstreels, Gilles Delie

The reference code for this position is 2025-016. Mention this reference code on your application form.