Advanced characterization of amorphous chalcogenide threshold switches for self-selective memory applications

Leuven | More than two weeks ago

Exploring polarity-dependent effects in Ovonic Threshold Switching (OTS) materials to enable next-generation cross-point memory

Context

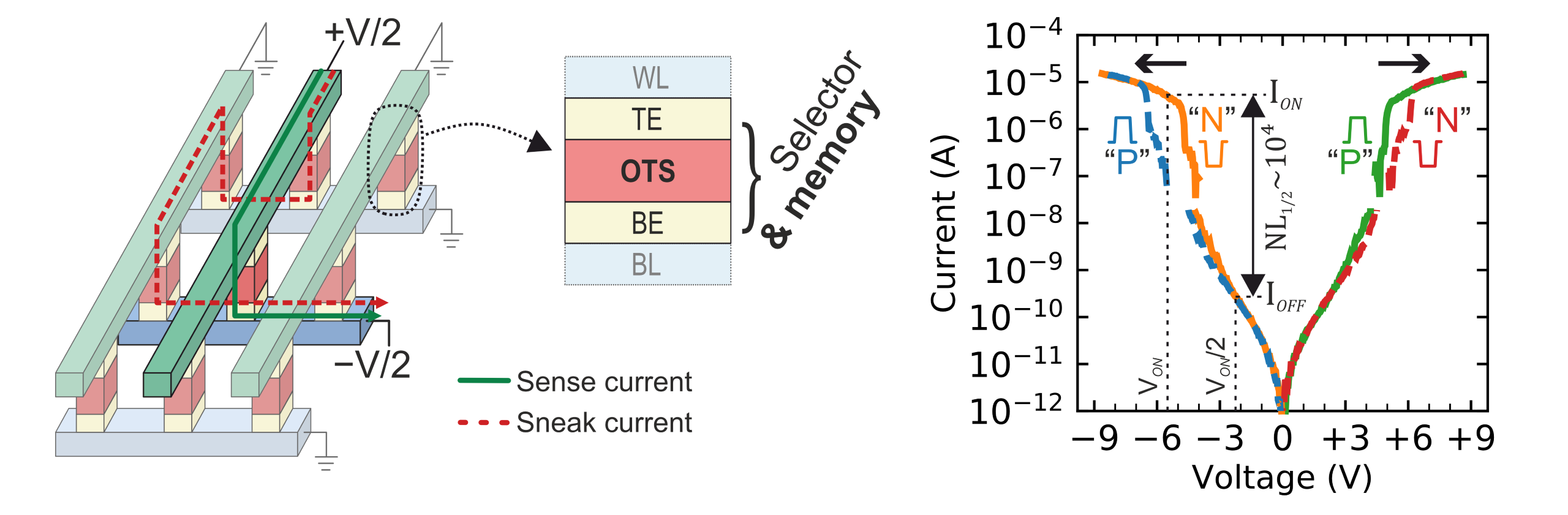

Chalcogenide materials have long been considered for use in memory applications, with the most notable example being the Phase-Change Memory (PCM). In combination with a two-terminal selector device, typically also chalcogenide-based Ovonic Threshold Switch (OTS), a compact cross-point array can be realized to achieve high-density memory [1]. However, PCM-based cross-point memory suffers from a number of issues inherent to the phase change process, hampering its commercial adoption. Namely, high programming current required to melt and amorphize the material during RESET, and slow programming speed necessary to crystallize it during SET operation. Moreover, co-integration of OTS and PCM is challenging from the fabrication point of view, limiting the possibility for scaling and 3D integration.

To address these issues, imec has pioneered a novel self-selective memory (SSM) technology, consisting of simple OTS-only cell [2]. It relies on the polarity effect in amorphous chalcogenides, manifested as an increase in the threshold voltage (Vth) whenever the polarity of the applied pulse changes [3]. It offers good scalability, high-speed capability, all with a possibility of low-power operation. Thanks to its unique properties, SSM technology has attracted significant attention from the industry in the recent years [4-6]. While having a clear application potential, at the moment the fundamental understanding of the polarity effect is still lacking, which is essential to enable further technology development.

Objective

The aim of this project is to gain insight into the origin of the memory effect in SSM device. This is to be achieved by performing advanced electrical characterization (DC and pulsed measurements) under various operating conditions (programming speed, current, temperature, etc.) to establish the performance-limiting factors. The goal is to use these results to guide the development of SSM technology, in cooperation with a team of device, simulation and process experts.

Requirements

- Deep knowledge of semiconductor device physics, familiarity with memory technologies

- Data analysis skills, working knowledge of Python (or other scripting language)

- Experience with electrical characterization instrumentation is a plus

References

[1] A. Fazio, “Advanced Technology and Systems of Cross Point Memory,” in 2020 IEEE International Electron Devices Meeting (IEDM), Dec. 2020, p. 24.1.1-24.1.4. doi: 10.1109/IEDM13553.2020.9371976.

[2] T. Ravsher et al., “Self-Rectifying Memory Cell Based on SiGeAsSe Ovonic Threshold Switch,” IEEE Trans. Electron Devices, vol. 70, no. 5, pp. 2276–2281, May 2023, doi: 10.1109/TED.2023.3252491.

[3] T. Ravsher et al., “Polarity-dependent threshold voltage shift in ovonic threshold switches: Challenges and opportunities,” in 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA: IEEE, Dec. 2021, p. 28.4.1-28.4.4. doi: 10.1109/IEDM19574.2021.9720649.

[4] S. Hong et al., “Extremely high performance, high density 20nm self-selcting cross-point memory for Compute Express Link,” in 2022 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 2022, p. 18.6.1-18.6.4, doi: 10.1109/IEDM45625.2022.10019415.

[5] I.-M. Park et al., “Enhanced Endurance Characteristics in High Performance 16nm Selector Only Memory (SOM),” in IEEE International Electron Devices Meeting 2023, San Francisco, CA, USA, Dec. 2023, p. 21.7.1-21.7.4.

[6] J. Lee et al., “Enhancing Se-based Selector-only Memory with Ultra-fast Write Speed (~10 ns) and Superior Retention Characteristics (> 10 years at RT) via Material Design and UV Treatment Engineering,” in IEEE International Electron Devices Meeting 2023, San Francisco, CA, USA, Dec. 2023, p. 21.6.1-21.6.4.

Type of project: Combination of internship and thesis, Internship

Duration: 3-6 months

Required degree: Master of Science, Master of Engineering Science

Required background: Nanoscience & Nanotechnology, Electrotechnics/Electrical Engineering, Physics, Materials Engineering

Supervising scientist(s): For further information or for application, please contact: Taras Ravsher (Taras.Ravsher@imec.be) and Daniele Garbin (Daniele.Garbin@imec.be)

Only for self-supporting students.