Building a large-scale physical quantum computer is still challenging. When scaling up qubits, wiring diagrams get increasingly more complicated. Bogdan Govoreanu, quantum computing program manager at imec, presents a smart way of interconnecting neighboring silicon qubits in a 2D bilinear array. This architecture tackles the qubit connectivity problem and is a potential pathway for realizing a quantum computer. The array design, together with device geometrical requirements analysis based on advanced multiscale modeling, is presented in a paper at IEDM 2021.

How to build a large quantum computer

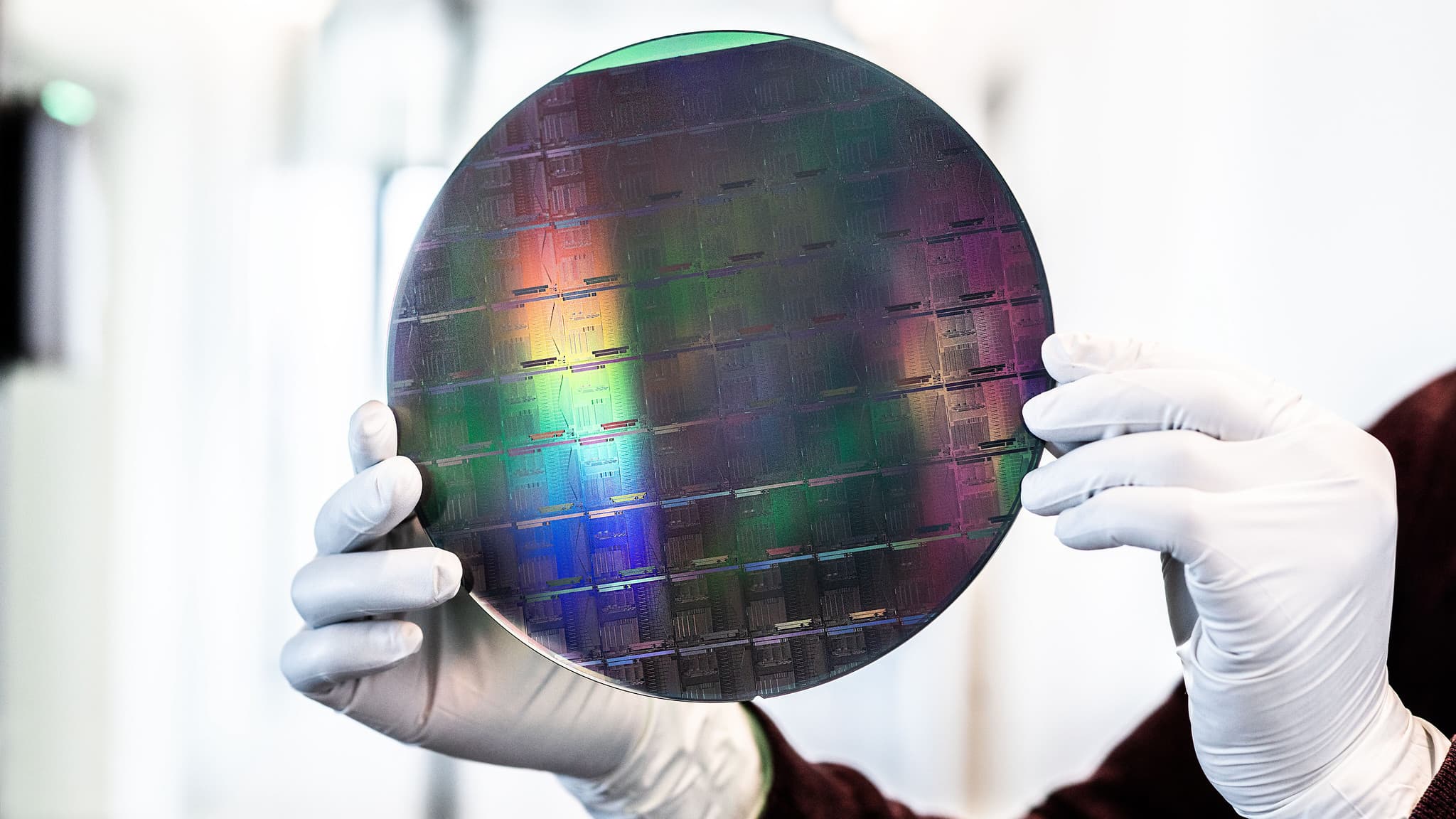

Quantum computers leverage the properties of quantum physics to process larger amounts of data significantly faster than classical computers. The basic units, quantum bits or qubits, simultaneously exist in two states making it possible to sift through a vast number of potential outcomes at once. Silicon-based qubits are very attractive for potential use in quantum computers because they are compatible with the well-established processes of high-volume manufacturing in the semiconductor industry. Nevertheless, scaling up the number of qubits remains a roadblock for building large-scale quantum computers. While small arrays have been demonstrated, a practical design that scales to the requirements where it outperforms classical computers is still lacking.

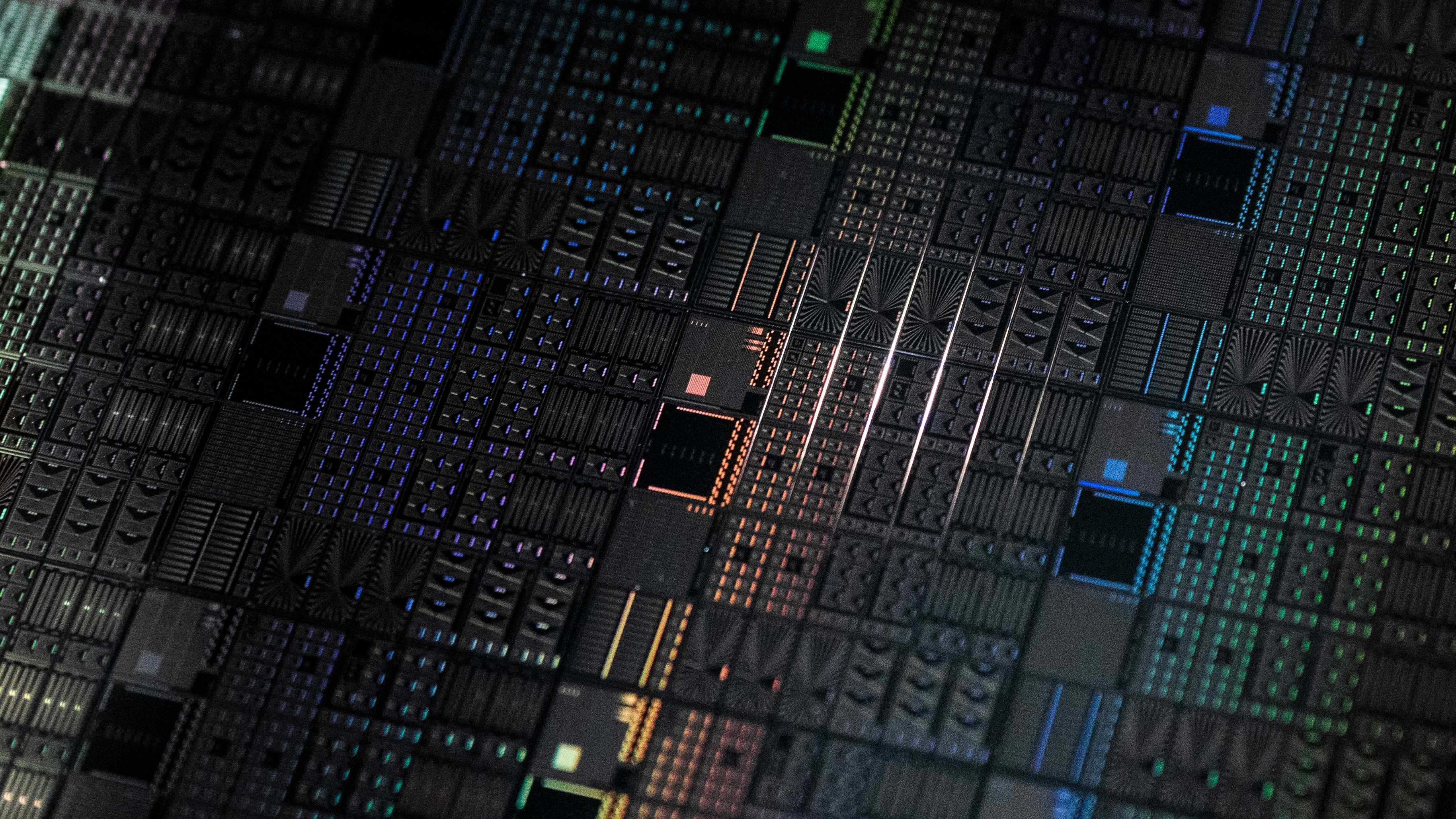

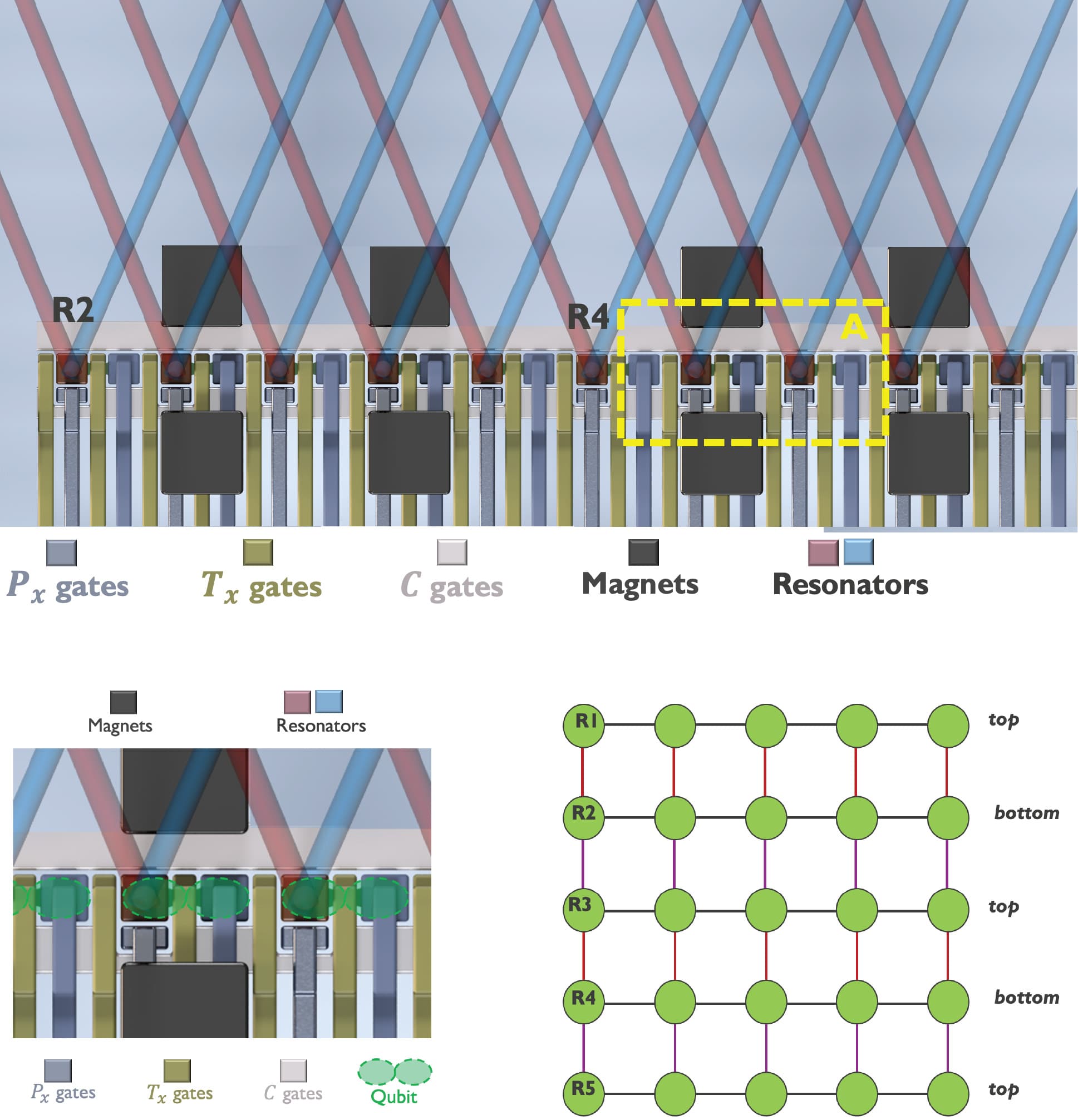

One bottleneck to developing larger quantum computers is the problem of how to arrange qubits. Efficient quantum algorithms require 2D-arrays where qubits can interact with their neighbors and be accessed by external circuits and devices. Each qubit needs dedicated lines for control and readout and a small pitch of typically tens of nanometers between two qubits. Increasing the number of qubits makes it therefore difficult to access the qubits at the center of the array. “We propose an elegant solution to this challenge: a bilinear 2D design for silicon qubits where each qubit connects to four other qubits,” tells Bogdan Govoreanu. “This architecture yields a compact array where different qubit coupling mechanisms are combined to achieve an overall connectivity of four, for each qubit in the bilinear array.”

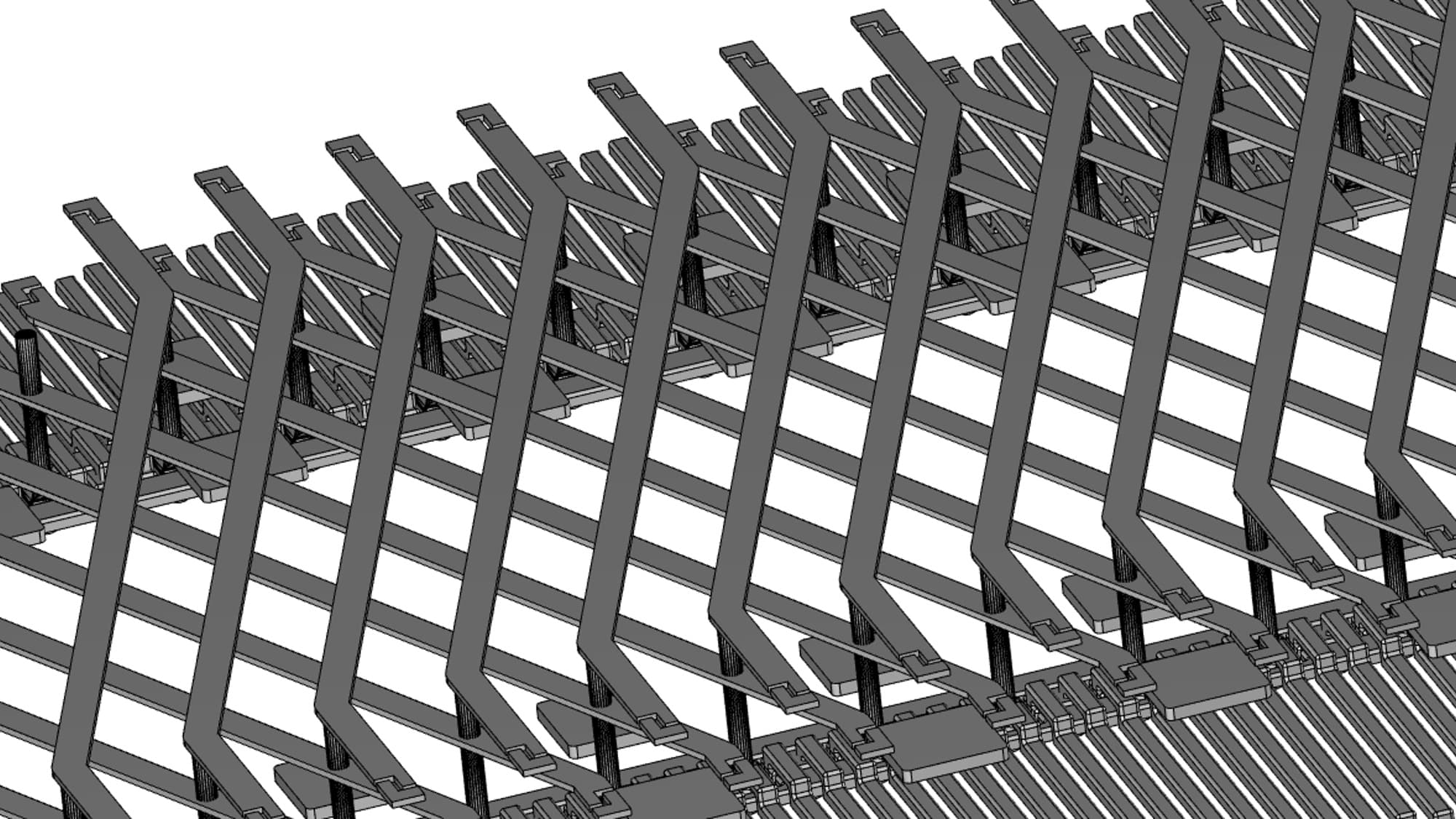

Figure 1: (top): Mapping of a square 2D lattice onto an equivalent bilinear array. Qubits are arranged physically into two parallel 1D arrays, which are interconnected through the top-bottom “photonic interconnections”, realized with superconducting resonators (shown in red and blue). (bottom): Zoomed-in area “A” (left), illustrating neighboring qubits within the same 1D linear array, which couple through the exchange interaction mechanism. Each qubit has an overall connectivity of four, just as if they were arranged in a 2D surface code compatible lattice (right).

Solving the qubit connectivity problem

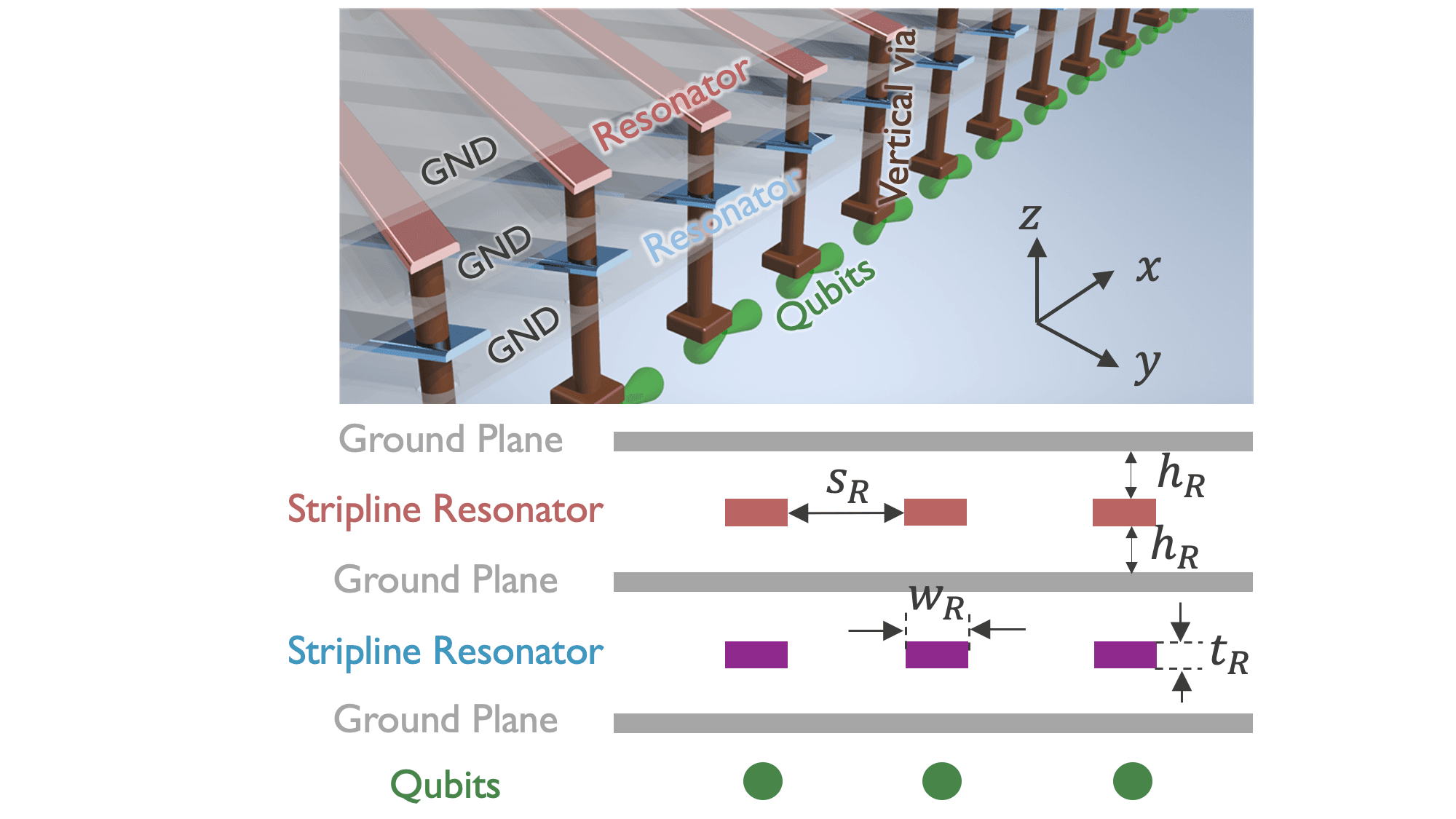

“Our design is based on topologically mapping a 2D square lattice, to form a so-called bilinear design, where alternating rows of the lattice are shifted into two rows or 1D arrays (see Figure 1). By arranging the qubits in two rows they always remain addressable while maintaining the target connectivity of four in the equivalent 2D square lattice array. These arrays are also easily scalable as we only need to grow them in one dimension, along the rows,” explains Bogdan Govoreanu. “The connections between the two 1D arrays do not intersect because they are wired on two different planes, separated by a ground plane to isolate them from each other (Figure 2).”

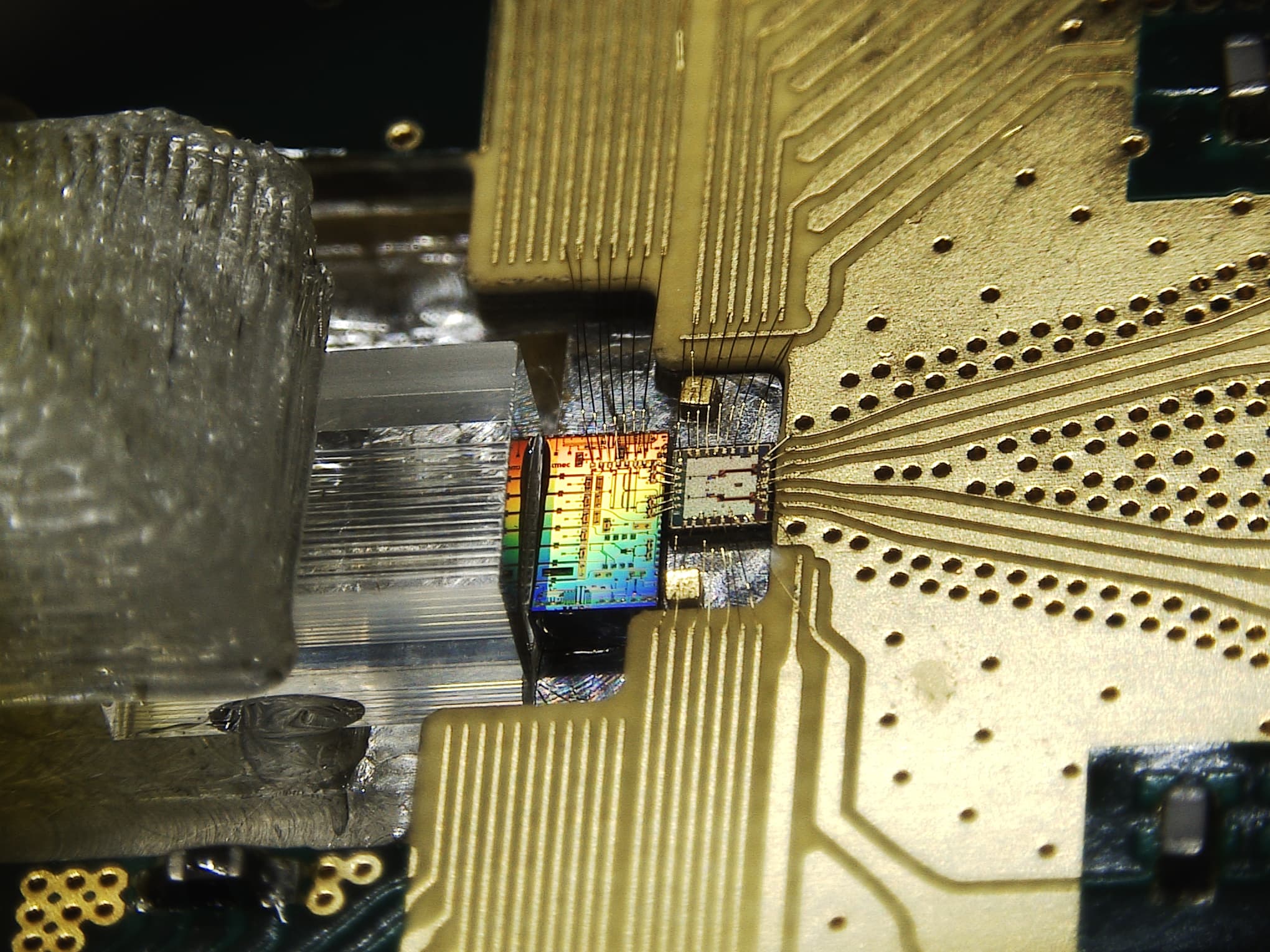

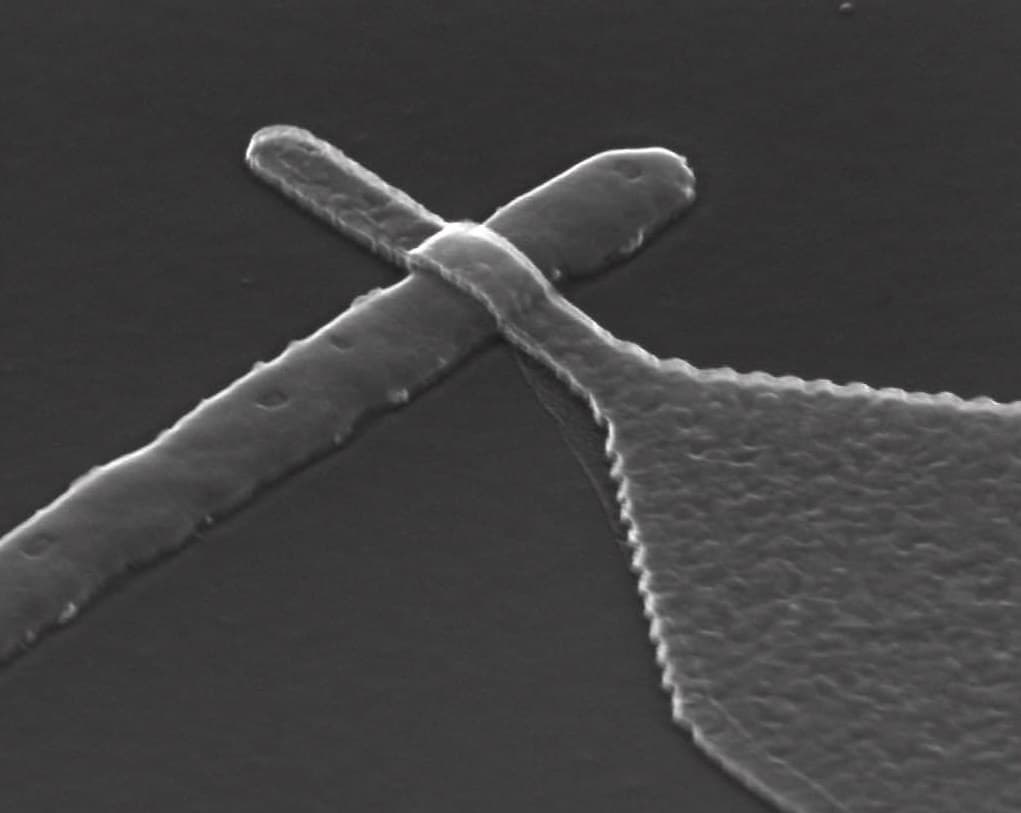

In this architecture, each qubit corresponds to the spin orientation of an electron confined in a potential well, called a quantum dot. Coupling these qubits is necessary for ‘quantum entanglement’, a property that underlies the exponential computing power of quantum computers. Entangled qubits store all the possible combinations of the quantum states of each qubit (e.g. for two qubits, this results in four values). The quantum dots within a 1D array are coupled through the spin interaction between electrons in nearby quantum dots, where nearby electron spins naturally interact through a quantum mechanical process called exchange coupling. The quantum dots between the 1D arrays are coupled over a long distance (~mm) via a microwave resonator, fabricated using superconducting materials. Such a long range is possible since the qubit state can be coupled to the photonic mode of the resonator, when the qubit electron is delocalized between two quantum dots.

Figure 2: Schematic of the resonators that connect qubits between 1D arrays. The resonators are placed in separate layers isolated by ground planes to avoid crossovers. Crosstalk between resonators in the same layer is minimized by ensuring sufficient spacings.

Tolerating errors

The quantum states are very fragile and prone to error. That is why building a large quantum computer is not just about scaling up the number of qubits, it is also about how resistant they are to errors. Since quantum computers cannot use the same error-correcting algorithms as classical computers, they fall back on quantum error correction techniques with ‘logical qubits’ - a complex arrangement of thousands of physical qubits that is used to encode a single qubit. “Our design is compatible with the widely accepted quantum error correction scheme, the surface code, that can run algorithms tolerating up to certain qubit error” explains Bogdan Govoreanu.

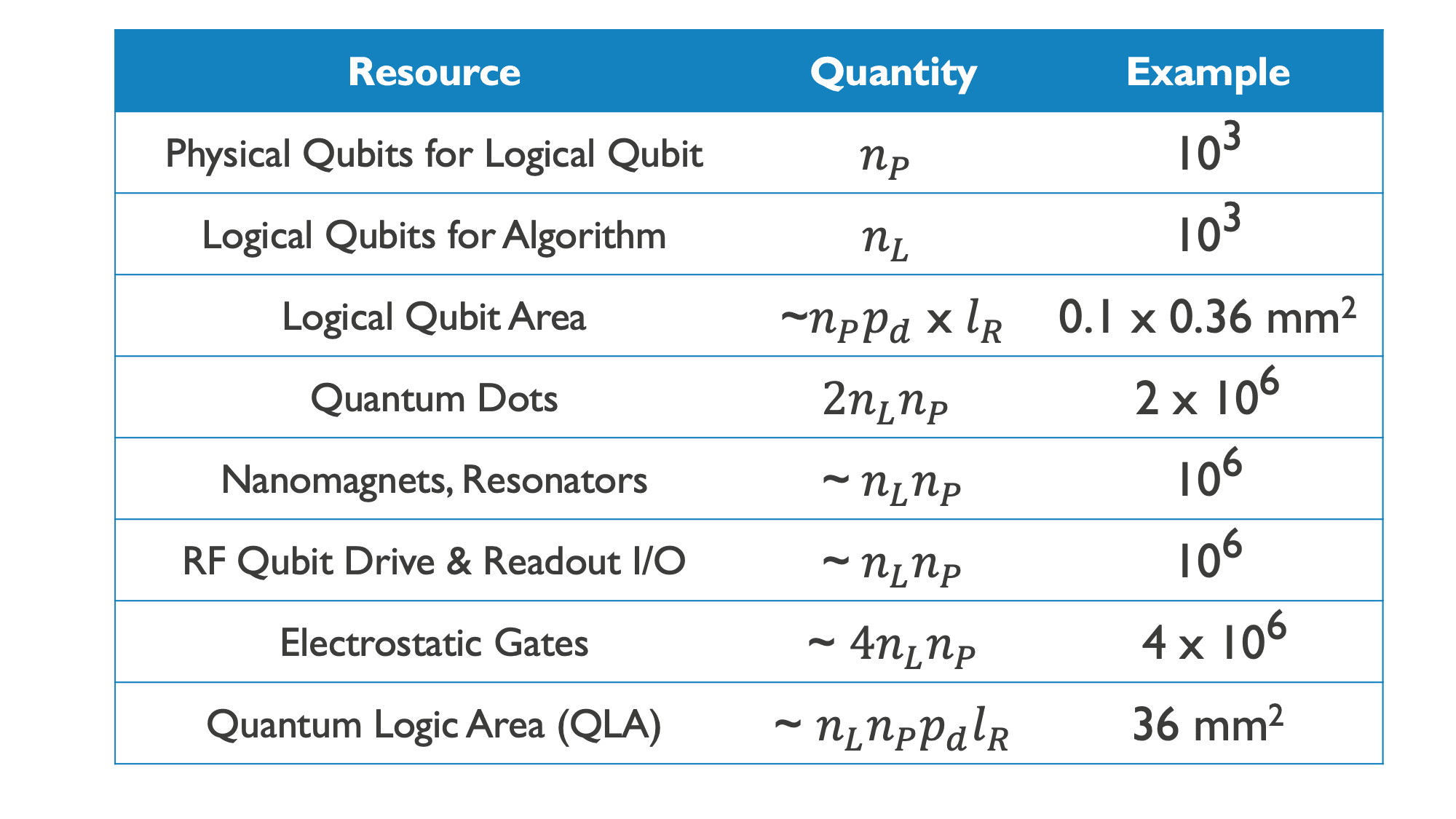

“The typical number of physical qubits to implement a logical qubit is believed to be somewhere between 103 to 104, depending on the quality of the physical qubits. Hundreds to thousands of logical qubits are necessary for running practical large-scale algorithms, which implies that overall physical qubit numbers can exceed a million. In this paper, we characterized the relevant quantum resources needed for viable quantum error correction, along with providing a detailed analysis of the required device dimensions, tolerable noise specifications and quantum gate operations times in the structure (Figure 3). The bilinear architecture needs an extremely compact quantum logic area of around 36mm2 even for a system with a million qubits. Moreover, the resonators and the electrostatic gates defining the quantum dots are easily accessible from both sides in the bilinear array, thereby considerably reducing the wiring fanout complexity.”

“This design is compatible with current CMOS fabrication technologies and can thus open the path for a future demonstration of large-scale silicon quantum computers,” concludes Bogdan Govoreanu.

Figure 3: Summary of the scaling of quantum components with number of qubits. For a system with a million qubits, only 36mm2 space is occupied, highlighting the compactness of the architecture.

Want to know more?

- Follow imec's presence at the 2021 IEEE International Electron Devices Meeting

- Read all details of the novel device architecture in the paper entitled “Large-Scale 2D Spin-Based Quantum Processor with a Bi-Linear Architecture” by F.A. Mohiyaddin, R. Li, S. Brebels, G. Simion, N. I. Dumoulin Stuyck, C. Godfrin, M. Shehata, A. Elsayed, B. Gys, S. Kubicek, J. Jussot, Y. Canvel, S. Massar, P. Weckx, P. Matagne, M. Mongillo, B. Govoreanu and I. P. Radu, presented at IEDM 2021, which can be requested here.

Bogdan Govoreanu is Quantum Computing Program Manager at imec, where he coordinates the technical research and development program activities. Prior to this, his research work included various topics in Memory Technology and Emerging Devices, with focus on Flash and resistive switching memory technologies, selectors and neuromorphic computing. He developed strong interests in novel concepts for computing and storage beyond current mainstream technologies. As of 2017, his research focuses on Quantum Computing Technologies and Systems. Bogdan holds a Ph.D. degree in Applied Sciences from KU Leuven for his research performed at imec on novel tunnel barrier concepts.

Published on:

11 December 2021