Parasitic resistance analysis for advanced CFET-based technology nodes.

PhD - Leuven | More than two weeks ago

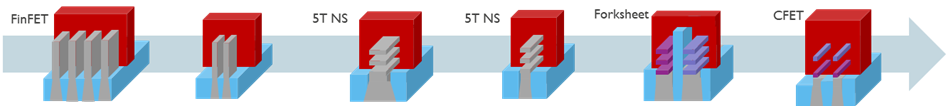

The aggressive downscaling of field-effect transistors (FETs) towards the Complementary FET (CFET) nanosheet (NS) based technology has led to a dramatic increase of the parasitic access resistance in logic devices. Today, the on-current is even significantly limited by this complex resistance contribution which is not controlled by the gate. Next to geometrical effects linked to the scaling of the device dimensions, the access resistance is also affected by adverse effects deteriorating materials deposited in small volumes. Consequently, tremendous research efforts are being devoted to developing new source-drain (S/D) semiconductor materials and contact metals.

Before their potential integration in devices, the physical properties of these new materials and their impact on electrical performance need to be evaluated and benchmarked in a systematic manner. Currently, this is mainly accomplished based on the Transmission Length Method (TLM) using dedicated test structures. However, given their relaxed dimensions, the latter are no longer well suited to evaluate the contact performance in advanced FETs. Indeed, S/D epitaxy and contact deposition processes are impacted by scaling effects which are difficult to reproduce in simplified structures.

The goal of this PhD project therefore is to gain insight into the contact resistance bottleneck through simulation-based analyses and dedicated experiments such that effective resistance reductions can be implemented in advanced CFET. To this end, the existing test structures will be critically evaluated through TCAD modeling such that improved short-loop solutions can be proposed. Based on these new test vehicles, a systematic evaluation of the confined S/D and contact process candidates will be performed. The PhD candidate will then identify the key contributors to the resistance, and gain insight into the impact of epi quality, confinement, strain, contact metal, silicides, as well as the source-channel and drain-channel hetero-interfaces, and steer the design and processing efforts towards reduced contact resistance.

In this exciting project at the forefront of advanced logic, the candidate will be supported by multidisciplinary teams including process, TCAD modeling, integration and metrology experts. By joining imec, the candidate will be part of an international team developing logic solutions for tomorrow. Imec is a place combining innovation and fundamental research, tightly bonded to applications and industrial partners. Through imec academy, the candidate will in addition have a wide range of training possibilities.

In summary, the PhD candidate will have opportunities to:

- realize an in-depth study of parasitic resistance components limiting the performance of CFET/NS based devices and propose solutions to overcome upcoming challenges.

- model and design a new-generation of short loop test-structures with realistic contact sizes and experimentally implement and demonstrate solutions leveraging existing and newly developed short loop test-structures.

- validate benefits on transistor test-structures.

- explore and analyse the fundamental limits of the CFET/NS technology in terms of parasitic resistances.

Required background: Electrical engineering, applied physics, nanoelectronics, material science

Type of work: 10% literature, 20% design, 10% processing, 30% electrical characterization and 30% modeling/simulation

Supervisor: Anne Verhulst

Co-supervisor: Pierre Eyben

Daily advisor: Pierre Eyben, Clement Porret, Philippe Matagne

The reference code for this position is 2025-002. Mention this reference code on your application form.