[NanoIC topic] Sustainable Design-Technology Co-Optimization for Advanced Technologies

PhD - Leuven | More than two weeks ago

Integrated circuits (ICs) have evolved to meet the needs of a changing society. While research initially focused on area scaling to decrease component cost, additional societal demands arose for increased performance (to enable more advanced applications) and later decreased power (to enable the mobile era). Together, these demands of Power, Performance, and Area form the PPA framework, which until recently has driven the design of new technology generations. Nevertheless, when moving towards increased process complexity and novel technologies, cost per area may increase significantly, making simple die area a poor metric for cost. Hence, more elaborate Cost modeling and optimization are required in the form of PPAC. Furthermore, the need for a sustainable society is driving demand for fabrication of electronic devices with low environmental impact. This raises questions of how we transition from PPAC to PPACE, introducing Environmental considerations into circuit design and manufacturing.

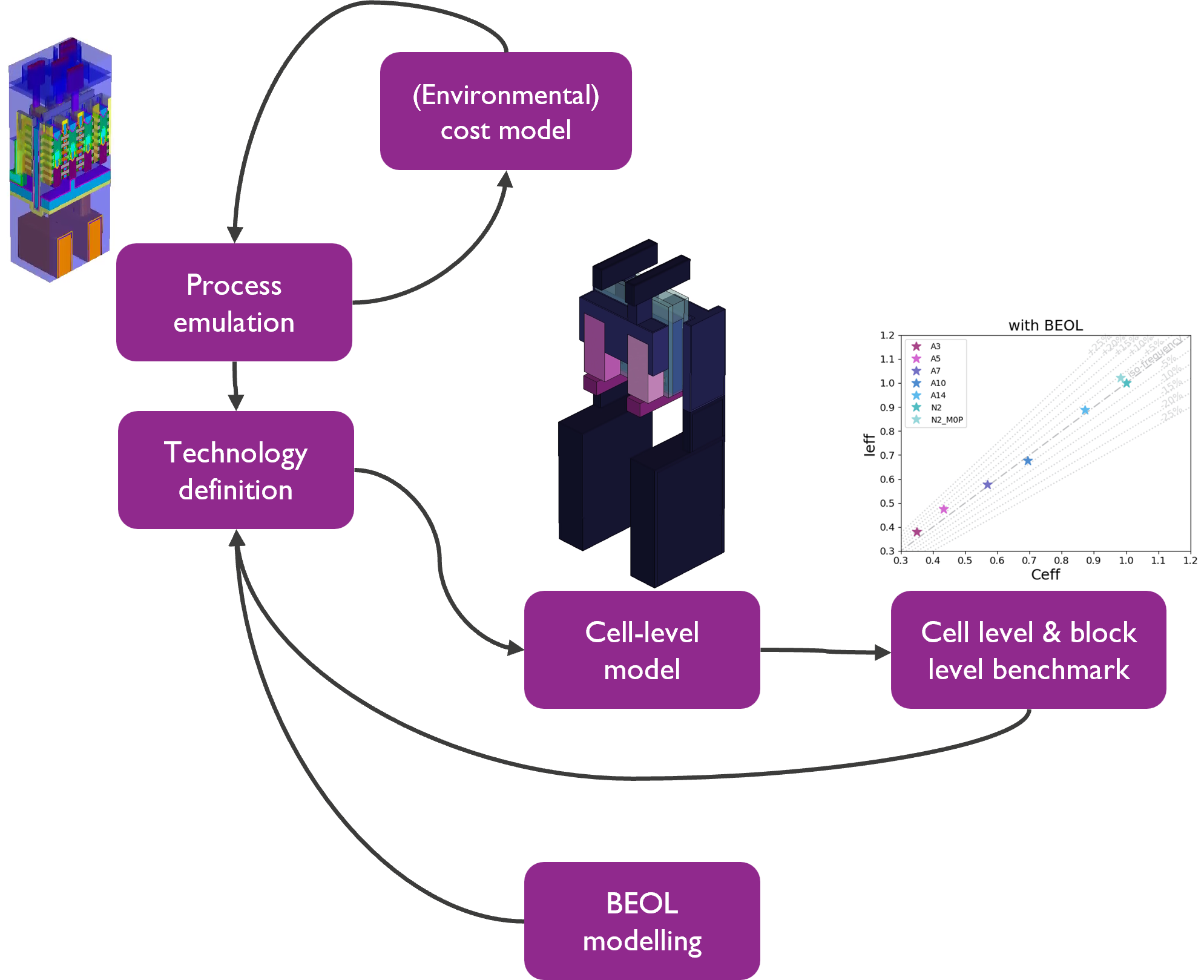

In this PhD, you will enable the transition from PPA to PPACE for the exploration of advanced technologies, such as CFET, 2D, and IGZO, taking into account the cost and environmental cost linked to integration and process assumptions.

You will study different device architectures and technologies, evaluating different design options as well as process integration flows. You will enhance cost modeling, incorporating detailed process integration flows, enabling improved feedback on technology options. Using this improved model, you will explore opportunities to optimize the process flow, reducing cost while maintaining power and performance.

You will investigate the various environmental impact of these technologies through life cycle assessment (LCA), and determine what changes in those impacts are needed to improve their sustainability. You will explore what those changes mean for device design and manufacturing, and identify easily adoptable ways to reduce environmental impact while still meeting the other PPACE requirements.

As reducing cost and/or environmental cost may impact PPA, trade-offs are imperative. You will assess these trade-offs for power, performance, cost and environmental cost, for different technologies and applications. Based on these trade-offs, you will couple back to the technology to find a global optimum for next-generation technology nodes. You will consider different flavors of the technologies, optimized within their context.

You will use and expand powerful in-house modeling software developed by imec, to assess and improve the PPA(CE) impacts of new technologies. You will focus on various aspects of design and manufacturing depending on background and interest. You will work with experts inside and outside imec to test your new device concepts, and to embed promising findings in industry.

Who you are

- You hold a master’s degree in nanotechnology, electrical engineering, material science or equivalent.

- You combine a strong interest in engineering and scientific research with a desire to see your work applied in industrial and academic collaborations. You are able to learn quickly and independently. You aspire to become an expert in your field, while simultaneously collaborating with other researchers and senior staff to efficiently generate state-of-the-art results.

- You have a background in integrated circuit design and/or semiconductor manufacturing and/or sustainability.

Required background: Nanotechnology, Electrical Engineering, Material Science or equivalent.

Type of work: 30% literature, 70% modeling/design

Supervisor: Kris Myny

Co-supervisor: Juergen Boemmels

Daily advisor: Anshul Gupta, Lynn Verschueren, Job Soethoudt

The reference code for this position is 2026-208. Mention this reference code on your application form.