PhD topic: Optimized buried epi channels for Quantum Computing applications

Leuven | More than two weeks ago

Contribute to the development of the highest quality 28Si/Si1-xGex Quantum Dot qubits by providing advanced deposition processes.

Microelectronics components are widely embodied in everyone’s daily life as they form the elementary bricks in multiple types of devices such as cars, smartphones, and not at least computers. Despite the extreme success of classical computers, there are mathematical problems which they cannot solve and for which quantum computing is the alternative solution. In quantum computing, the qubit forms the basic unit of information, similar to the conventional bit. Unlike a classical bit, a qubit can exist in a superposition of two "basis" states. Yet, if a physical qubit is not sufficiently isolated from its environment, noise will be introduced and eventually its characteristic quantum properties are lost.

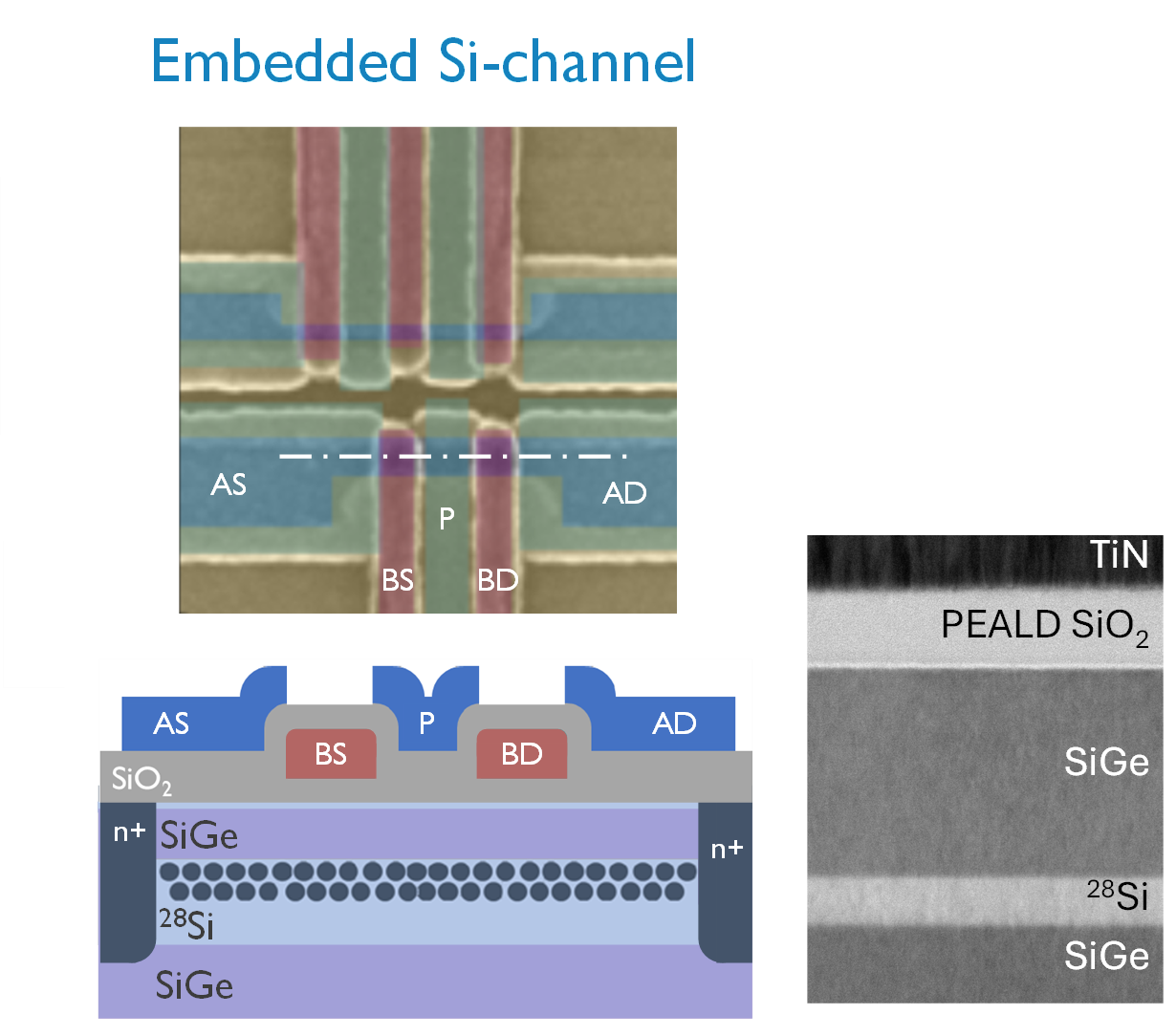

The Si-SiGe material system is one of the most promising quantum materials hosting electronic spin qubits in well-defined quantum dot geometries. Its compatibility with a large semiconductor ecosystem can be realistically leveraged towards the quantum scaling goals and the use of isotopically purified 28Si provides nuclear spin-free material enabling long spin lifetimes of the hosted spin qubits. However, tailoring Si and SiGe to quantum applications raises new challenges in material fabrication towards quantum-grade quality. The quantum devices require near-perfect isolation from the solid-state environment. Low defect density, low disorder, low charge noise etc. are crucial. While studied very much in depth for classical electronics applications, tailoring Si and SiGe to quantum applications comes with a series of novel challenges in view of epitaxial growth and material characterization: The assessment and improvement of (i) interface sharpness, (ii) lateral roughness, and (iii) the interface to the gate dielectric.

In this PhD, these challenges will be addressed by optimizing advanced material deposition processes based on epitaxial Chemical Vapor Deposition (CVD). The growth studies will be combined with advanced material characterization. E.g. to characterize the interface roughness and sharpness of SiGe/Si/SiGe heterostructures epitaxially grown on SiGe Strain Relaxed Buffers, the candidate will get access to external facilities to perform synchrotron-based reflectometry measurements which will be combined with in-house X-ray diffraction, X-ray reflectivity measurements, TEM, and atom probe tomography measurements.

More specifically, this PhD covers the following research topics:

- Optimizing the epitaxial Si/SiGe interface and the buffer layer

- Extraction and comparison of the interface roughness and sharpness of the top 28SiGe / buried 28Si-channel interface and study their impact on valley splitting.

- Reduction of the interface roughness and sharpness for better controllability of the valley splitting which eventually could also improve the qubit fidelity.

- Comparison of strain uniformity and defectivity inside the buried strained 28Si quantum well as this correlates with disorder and is reflected in mobility and percolation density.

- Optimizing the interface to gate dielectric

- Optimization of dielectric / Si-cap / 28SiGe material properties in terms of Si-cap thickness uniformity, and Ge segregation into the Si-layers and the resulting material quality in terms of deep traps inside the dielectric.

The PhD student will become a member of the Group IV epi team and will also collaborate with our device fabrication team. The latter will study how modifications in the epitaxial growth process affect quantum device performance. E.g. they study the valley splitting inside the buried strained 28Si QW, and the band line-up between 28SiGe and 28Si which are a strong function of the strain.

Required background: Physics, Microelectronics, or Material Science

Type of work: 50 experimental, 30% theoretical, 20% literature

Supervisor: Kristiaan De Greve

Co-supervisor: Roger Loo

Daily advisor: Yosuke Shimura

The reference code for this position is 2025-077. Mention this reference code on your application form.