Introduction

The IoT is fast becoming a multilevel system of systems spanning the globe. But to realize the growth path that is forecasted, we’ll need optimized and specialized hardware, capable of, amongst others, sensoring at ultralow power, guaranteeing a system’s security during its full lifetime, and learning from huge amounts of data. Imec’s Diederik Verkest and Ingrid Verbauwhede talk about the next step: how technology can be further optimized to solve specific system and application demands. As examples, Ingrid proposes hardware-entangled security and Diederik explains imec’s efforts in neuromorphic processing.

A heterogeneous chip future (Moore on steroids)

“Until recently,” says Diederik Verkest, “we concentrated almost all of our scaling effort on the smallest unit of a chip, the transistor, whatever that unit was used for afterwards. Next, to stay on the course predicted by Moore’s Law, we co-optimized technology with lower-level design units such as e.g. memory cells. Now we’re working our way up in the system hierarchy, always looking how we can optimize technology to better implement a function. So naturally, we also arrive at the key functions needed for the future IoT, such as a failsafe security. And we are also eying specialized processors for e.g. neuromorphic computing, complete subsystems to tackle specific, hard problems.”

Verkest adds that he is excited about imec’s recent merger: “This is a great opportunity for both sides. My new colleagues are application experts in domains such as bio-informatics or security. They can help us screen technology and direct us to the solutions that are best fit to solve the hard problems in their domains. And reversely, as application experts, they will learn from all the hardware opportunities that we are considering. What I see happening going forward, is a much more intimate, structured interaction between hardware and application R&D, greatly speeding up this system/technology co-optimization.”

Secure chips with unclonable fingerprints

Today already, electronics are embedded in many objects in our environment. Think of your car’s keys, security cameras, smart watches, or even implanted pacemakers. “This makes security considerably more complex than it used to be," says Ingrid Verbauwhede. "Existing cryptographic algorithms demand a lot of compute power, so they run mainly on high-end platforms. But most microchips in the IoT are small, lightweight, low-power and have a limited functionality. So traditional cryptography doesn’t fit well. Our ambition is to make chips that are inherently more secure through the way they are designed and processed."

In 2016, Ingrid Verbauwhede and her team received a prestigious European ERC research grant for their Cathedral project.

“This grant is at once a recognition for what we have been doing, and a great support going forward. A support that will allow us to independently look for the best solutions.”

Ingrid’s team is exploring various ways of doing that:

“In the past, R&D looked at dedicated design methods for e.g. low-power chips. We now want to do the same to better secure chips. Chips e.g. that don’t leak information while they are computing so they are more resistant against side-channel attacks. And another of our focus points is implementing future-proof cryptography, algorithms that will protect a system during its long lifetime, even if it is attacked by future quantum computers.”

Asked for her plans for 2017, Ingrid Verbauwhede points to the direct access her team now has to technology processing at imec’s fabs:

“One of the characteristics of today’s chip scaling is process variation: each chip is slightly different from all others. From a reliability perspective, that is a nuisance. It requires engineers to take extra measures so that computations remain predictable. But there is also an upside that we want to exploit: the variations are like a fingerprint, a way to uniquely identify each chip without expensive calculations. It is what we call a physically unclonable function (PUF). And if you tie that function to the software running on the processor, you have another layer of security which is well-suited for IoT devices.”

Smart chips with brain power

Our brains are formidable computing wonders, using only a fraction of the power of traditional computers to obtain comparable results. Therefore, engineers are eager to mimic the brain on chip, e.g. to speed up deep learning from massive amounts of data, or low-power image recognition.

“But to do so,” says Diederik Verkest, “we have to replicate the brain’s architecture, a tight interconnection of an enormous number of relatively primitive processing nodes (the neurons) and their interconnections (the synapses). That is usually done with some type of crossbar architecture, wires laid out in a matrix (or cube), so that each input line connects with all outgoing lines. At a crossing of two lines, there is a switch that implements the synapses. They contain the intelligence of the system, the ability to hold data, process and learn from experience. So they should be made programmable and self-adaptable.

Work on this emerging domain at imec started some two years ago, partly embedded in the European Horizon2020 project NeuRAM3. In 2016, we have selected an architecture and screened options to implement the self-adapting synapses. We are convinced that our concept is uniquely suited to tackle the problem, so we’ve taken out a patent and are now building a proof-of-concept. In 2017, we will tape-out a first chip and package it into a neuromorphic computing system that we can test against neuromorphic application simulators with growing numbers of neurons.”

These brain-on-chips may not be exact copies of our brain circuits, but nature teaches us that it is physically possible to build much better computers than we do today. Computers that we need to make sense from the enormous amounts of data that the IoT will generate. But also for the intelligent sensors and robots of the connected world. Small, low-power, long-lasting devices that have to stand their ground among an ever growing stream of data, continuously adapt themselves to their environment, even learn and become smarter over their life time.

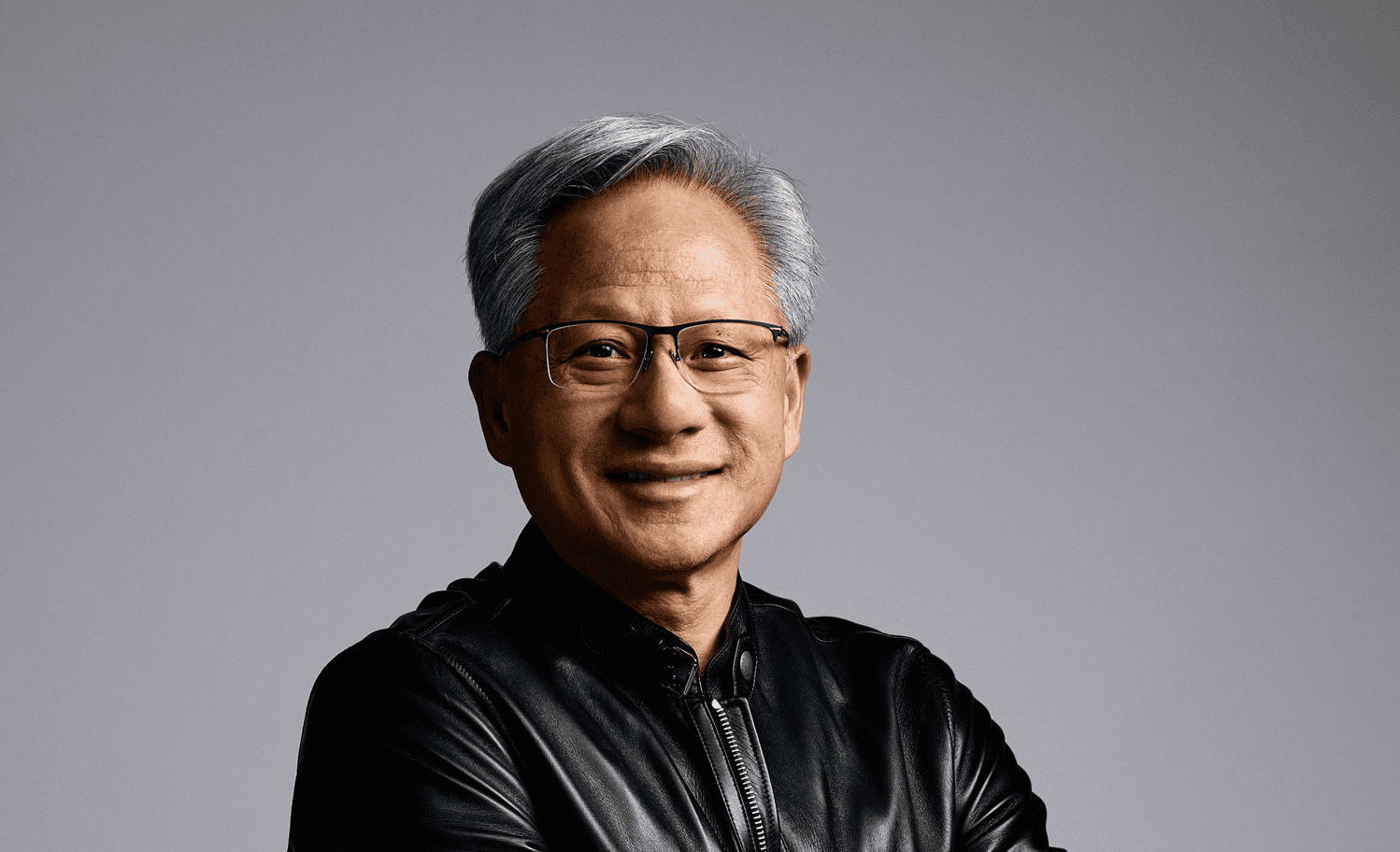

Diederik Verkest is director of imec’s INSITE program. After earning a Ph.D. in micro-electronics engineering from the KU Leuven, Diederik joined imec in 1994, where he has been responsible amongst others for hardware/software co-design. In 2009, he started imec’s INSITE program focusing on co-optimization of design and process technology for sub-14nm nodes. The program offers the fabless design community insights into advanced process technologies and provides a platform for foundries and fabless companies to discuss directions for next generation technologies.

Diederik Verkest published over 150 articles in international journals and at international conferences. Over the past years he has been involved in numerous technical conferences. He was the general chair of, DATE, the Design, Automation, and Test in Europe conference in 2003. Verkest is a Golden Core member of IEEE Computer Society.

Ingrid Verbauwhede is professor at the KU Leuven (Belgium) in the imec-COSIC research unit where she leads the embedded systems and hardware group. She is also adjunct professor at the electrical engineering department at UCLA, Los Angeles (USA).

Ingrid Verbauwhede is an IEEE fellow, member of IACR and she was elected as member of the Royal Academy of Belgium for Science and the Arts in 2011. Her main interest is in the design and design methods for secure embedded circuits and systems. She has published around 70 papers in international journals and 260 papers at international conferences. She is also inventor on 12 issued patents.

Published on:

1 January 2017