VLSI Symposium 2023

June 11 - 16, 2023 | Kyoto, Japan

Rebooting Technology and Circuits for a Sustainable Future

Imec is present at the 2023 Symposium on VLSI Technology and Circuits with 15 accepted papers, of which 13 first authored, including 1 invited.

Additionally, imec will host a workshop at VLSI 2023 with prominent speakers from Google, Intel, ASML, ARM, Cadence, Synopsys and Georgia Institute of Technology. This workshop aims to give an overview of the state-of-the-art of backside power delivery networks (BSPDN), by reviewing its open challenges and providing an outlook on the future research directions towards functional backside. Naoto Horiguchi, director CMOS device technology, will also give a short course on CMOS scaling by backside power delivery. Finally, imec presents four papers that add insights to its research on backside power delivery. Eric Beyne, fellow at imec, presents possible integration flows and challenges, such as nano-Through Silicon Vias (nTSV) for BSPDN. A joint paper with Arm evaluates the impact of backside power delivery on the implantation of a commercial 64-bit processor block at the N2 and A14 node. Next, imec discusses upcoming challenges of ESD reliability in DTCO with BSPDN routing via Buried Power Rails (BPR). Finally, imec evaluates power-performance-area (PPA) trade-offs and integration challenges of three types of backside power connections.

Highlights

Backside power delivery networks (BSPDN) is a prominent topic at this year’s VLSI. Imec is playing a pivotal role, providing an outlook on the future research directions towards functional backside. Learn more about this disruptive technology idea through the short course, workshop and papers listed below.

Short course – Advanced CMOS Technologies for 1 nm & Beyond

CMOS Scaling by Backside Power Delivery, Naoto Horiguchi, director CMOS device technology

Abstract

Current CMOS chips have both signal routing and power delivery in frontside of wafer. However, frontside power delivery has to go through multiple metal layers and wide power metal lines consume area, which cause IR drop and routing congestions, respectively. It is an attractive option to separate signal routing in frontside and power delivery in backside. It improves routing congestions and IR drop. Several backside power delivery options are proposed, and they have trade-offs in terms of process complexity, area scaling and IR drop. Backside power delivery integration requires extreme wafer thinning and metal connection from backside, which could cause challenges in integration control, such as wafer distortion and litho alignment, and device performance, such as channel stress and self-heating. Backside power delivery concept could be extended to functional backside, such as backside global interconnect and backside device, which enables further CMOS scaling by using backside engineering.

Workshop – Towards Functional Backside: What’s Next After Backside Power Delivery?

Organized by imec, with speakers from Google, Arm Intel, Georgia Institute of Technology, Cadence, Synopsys and ASML

Abstract

Technology scaling is driven by a constant need for better system performance, however, it also leads to significant power integrity and congestion bottlenecks. A major culprit for this is identified in the Back-End-of-Line (BEOL) scaling, i.e. interconnect wall, running into hard physical and technological limitations. Increased power density and high-resistivity metal layers are inherent challenges when designing the on-chip Power Delivery Network (PDN) to maintain IR drop within reasonable margins. Similarly, increasingly smaller standard cells pose a significant struggle when it comes to signal routing and pin access, also limiting the SoC performance. Functional backside is a disruptive technology idea with the potential to pave a path toward conquering these issues. Backside PDN has already shown tremendous power integrity improvements, and backside signaling has likewise proven to be a powerful tool for optimizing specific physical design tasks. In this workshop, we aim to give an overview of the state-of-the-art of this technology, by reviewing its open challenges and providing an outlook on the future research directions; spanning from the process and integration, to the EDA tools and algorithms, and to the impact on different applications and systems.

Papers – Highlight, BSPDN and DTCO sessions

- Nanosheet-based Complementary Field-Effect Transistors (CFETs) at 48nm Gate Pitch, and Middle Dielectric Isolation to Enable CFET Inner Spacer Formation and Multi-Vt Patterning, H. Mertens, et

Abstract

We report on Si nanosheet monolithic Complementary Field-Effect Transistors (CFETs) at industry-relevant 48nm gate pitch, with source-drains (SDs) and SD contacts formed for either bottom or top devices. SD epi patterning at 30nm vertical N-P space and high-aspect-ratio SD contact formation are successfully demonstrated. Functional devices with excellent subthreshold slope (SSSAT=70-75mV/dec) are reported for bottom and top devices, for both N- and PMOS. Middle dielectric isolation (MDI) formed by SiGe replacement processing is introduced as an enabler for monolithic CFET inner spacer formation and multi-Vt patterning.

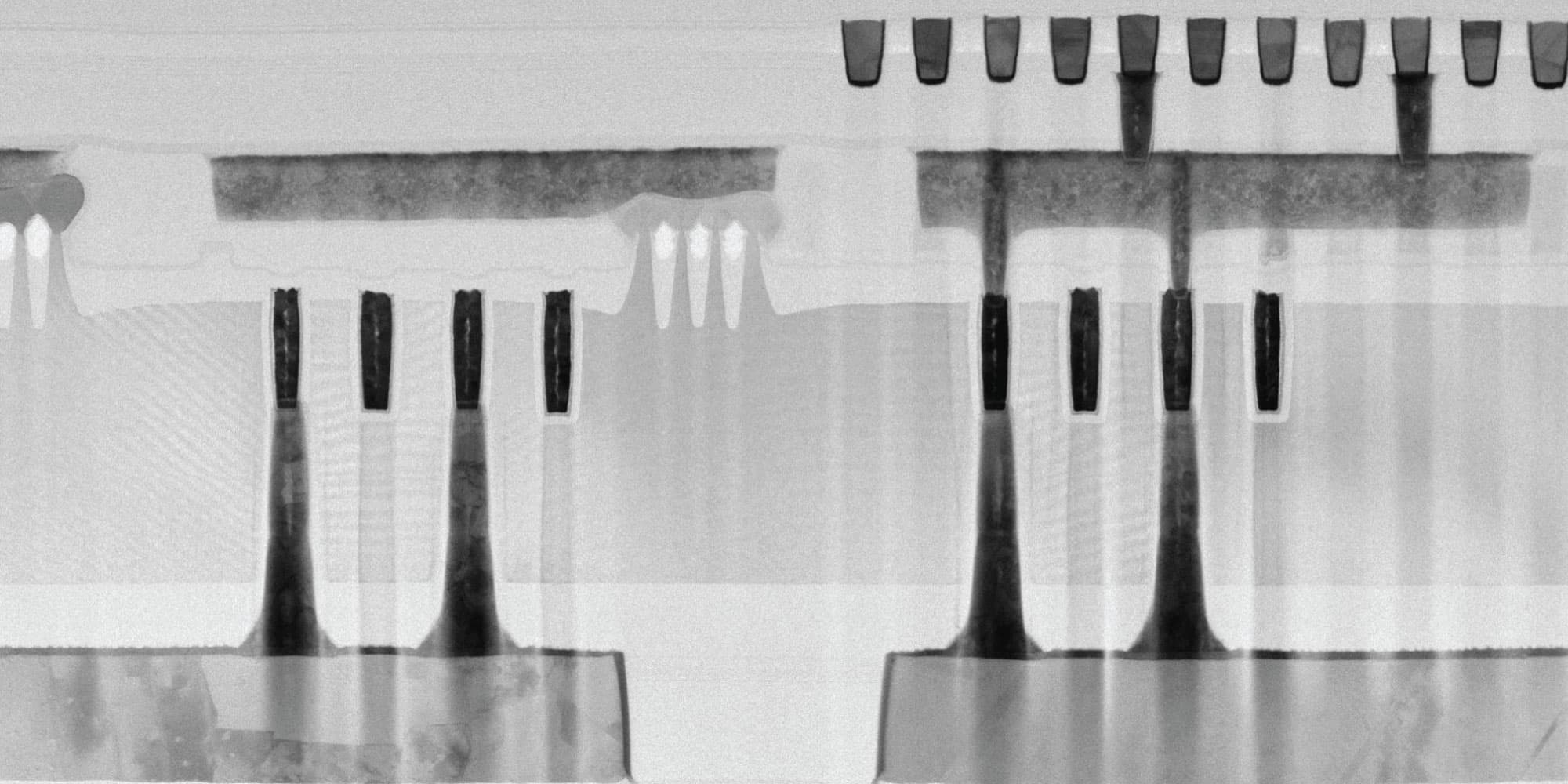

- Nano-Through Silicon Vias (nTSV) for Backside Power Delivery Networks (BSPDN), E. Beyne et al.

Abstract

In this paper we discuss the driving forces for moving to chip backside power delivery. Possible integration flows and challenges are discussed for integrating through-silicon via (TSV) connections that directly interconnect the chip at the standard-cell level. These approaches use power rail integration schemes that can be “buried” in the STI and Si below the devices or directly integrated as backside metallization scheme on the wafer backside. Both nTSV “last” and “first” integration flows have been demonstrated. Key technology challenges are the extreme wafer thinning required and back-side lithography correction to compensate for wafer distortions caused by wafer processing and W2W bonding.

- Block-level Evaluation and Optimization of Backside PDN for High-Performance Computing at the A14 Node, G. Sisto et al.

Abstract

This paper evaluates the impact of backside power delivery on the physical implementation of a commercial 64-bit highperformance block from ARM™ at the A14 node. A backside BEOL, including nTSV connections, is proposed and calibrated using TCAD and experimental data. The developed stack is modeled in a commercial cell-level parasitic extraction tool to enable its use during place and route. The same benchmark is physically implemented using imec's own A14 PDK. The backside PDN enables frequency improvements from 2% to 6% compared to the frontside PDN, stemming from a core area reduction from 8% to 23%. These results are obtained without negatively impacting the total power and simultaneously limiting dynamic IR drop below 35mV. Furthermore, different TSV options have been studied to potentially boost the IR drop gains up to 23%

- PPA and Scaling Potential of Backside Power Options in N2 and A14 Nanosheet Technology, S. Yang et al.

Abstract

This paper evaluates Power-Performance-Area (PPA) tradeoffs and integration challenges of three types of backside power connections: Through Silicon Via in the Middle Of Line (TSVM), Self-Aligned Front-to-Back via (BPR) and Backside contact (BSC) for nanosheets at N2 and A14 nodes. From TSVM to BPR to BSC, solid PPA gains are shown for High Density Logic, at the expense of increased process complexity. While TSVM remains competitive in N2 7-Track high-performance technology, BSC shows maximal gains in A14 5-Track high density node.

- Upcoming Challenges of ESD Reliability in DTCO with BS-PDN Routing via BPRs, W.-C. Chen (KU Leuven and imec), et al.

Abstract

In this paper, the impact of double-sided connectivity and buried power rails (BPR) on electrostatic discharge (ESD) diodes is reported. Connection from the backside and BPRs can change ESD current path and uniformity. It also introduces parasitic capacitance and layout penalty to ESD diodes. The ESD performance is strongly dependent on layout styles. Guidelines for a better layout style of double-sided connectivity cooperating with BPRs are proposed.

Circuits Session 5 – Wireless Transceivers

- An 8.7 mW/TX, 21 mW/RX 6-to-9GHz IEEE 802.15.4a/4z Compliant IR-UWB Transceiver with Pulse Pre-Emphasis Achieving 14mm Ranging Precision, M. Song, et al.

Abstract

This work presents an IEEE 802.15.4a4z compliant IR-UWB transceiver for high-precision ranging. By virtue of the proposed digital deserialization-serialization, the TX can generate the Inter-Symbol-Interference (ISI) free IEEE 802.15.4a4z packet. The proposed analog Finite Impulse Response (FIR)-based TX pre-emphasis improves 3.5x ranging precision without substantial power overhead and fulfills the spectrum requirement of the standard and the worldwide UWB regulations. The presented transceiver consumes 8.7 mW in TX mode and 21 mW in RX mode.

Evening Panel Discussion 1- What is Scalable & Sustainable in the Next 25 Years?

With Sri Samavedam, senior vice president CMOS technologies at imec, as panelist alongside speakers from Google, TSMC, Applied Materials, SK Hynix, moderated by Tokyo Electron and organized by NanoBridge Semiconductor and Google.

Overview imec contributions

Sunday, 11 June, 2023

Workshops

Towards Functional Backside: What’s Next After Backside Power Delivery?

Organized by imec, with speakers from Google, ARM, Intel, Georgia Institute of Technology, Cadence, Synopsys and ASML

The Deployment of Materials to System Co-Optimization Methodology (MSCO) to Enable Rapid PPACt Assessment for Advanced Node Technology Development

Organized by Applied Materials, with an imec presentation about Building a Methodology for Design- and System-Technology Co-Optimization by Naoto Horiguchi, director CMOS device technology.

Monday, 12 June, 2023

Short course - Advanced CMOS Technologies for 1 nm & Beyond

- CMOS Scaling by Backside Power Delivery, Naoto Horiguchi, director CMOS device technology

Demo session

- PPA and Scaling Potential of Backside Power Options in N2 and A14 Nanosheet Technology, S. Yang et al.

- Comprehensive 300 mm Process for Silicon Spin Qubits with Modular Integration, A. Elsayed et al.

Tuesday, 13 June; 2023

Technology session 1 – Highlight 1

- Nanosheet-based Complementary Field-Effect Transistors (CFETs) at 48nm Gate Pitch, and Middle Dielectric Isolation to Enable CFET Inner Spacer Formation and Multi-Vt Patterning, H. Mertens, et al.

Circuits Session 5 – Wireless Transceivers

- An 8.7 mW/TX, 21 mW/RX 6-to-9GHz IEEE 802.15.4a/4z Compliant IR-UWB Transceiver with Pulse Pre-Emphasis Achieving 14mm Ranging Precision, M. Song, et al.

Technology Session 4 – DTCO

- PPA and Scaling Potential of Backside Power Options in N2 and A14 Nanosheet Technology, S. Yang, et al.

- Upcoming Challenges of ESD Reliability in DTCO with BS-PDN Routing via BPRs, W.-C. Chen (KU Leuven and imec), et al.

Circuits Session 8 – Biomedical Circuit and Systems

- A Fingertip-Mimicking 12×16 200μm-Resolution e-skin Taxel Readout Chip with Per-Taxel Spiking Readout and Embedded Receptive Field Processing, M. D. Alea (KU Leuven) et al. –co-authored by imec

Technology Session 6 – Logic Technology 1: Advanced Platforms and Device Structures

- Molybdenum Nitride as a Scalable and Thermally Stable pWFM for CFET, H. Arimura et al.

- Integration of a Stacked Contact MOL for Monolithic CFET, V. Vega-Gonzalez et al.

Evening Panel Discussion 1- What is Scalable & Sustainable in the Next 25 Years?

With Sri Samavedam, senior vice president CMOS technologies at imec, as panelist alongside speakers from Google, TSMC, Applied Materials, SK Hynix, moderated by Tokyo Electron and organized by NanoBridge Semiconductor and Google.

Thursday, 15 June, 2023

Circuits Session 18 – Data Conversion Techniques

- A 3-320 fJ/Conv.step Continuous Time Level Crossing ADC with Dynamic Self-Biasing Comparators Achieving 61.4 dB-SNDR, M. Timmermans (Eindhoven Univ.) et al. – co-authored by imec

Technology Session 13 – Quantum Computing and Cryo-CMOS

- Comprehensive 300 mm Process for Silicon Spin Qubits with Modular Integration, A. Elsayed et al.

Technology Session 14 – New Channel Material 2: InOx and 2D Material

- Integration of Epitaxial Monolayer MX2 Channels on 300mm Wafers via Collective-Die-To-Wafer (CoD2W) Transfer, S. Ghosh et al.

- Towards Low Damage and fab-Compatible Top-Contacts in MX2 Transistors Using a Combined Synchronous Pulse Atomic Layer Etch and Wet-Chemical Etch Approach, S. Kundu, et al.

Technology Session 16 – Logic Technology 3: Advanced Platforms and Processes

- Novel Low Thermal Budget CMOS RMG: Performance and Reliability Benchmark Against Conventional High Thermal Budget Gate Stack Solutions, J. Franco et al.

Technology Session 17 – New Channel Material 3: IGZO

- Lowest IOFF < 3×10-21 A/μm in Capacitorless DRAM Achieved by Reactive Ion Etch of IGZO-TFT, A. Belmonte, et al.

Technology Focus Session 2 – BEOL/BSPDN

- Nano-Through Silicon Vias (nTSV) for Backside Power Delivery Networks (BSPDN), E. Beyne et al.

- Block-level Evaluation and Optimization of Backside PDN for High-Performance Computing at the A14 Node, G. Sisto et al.