IEDM 2021

December 11 - 15, 2021 | hybrid event

Event details

This year, imec has a strong presence at the 2021 IEEE International Electron Devices Meeting as (co-)author of no less than 21 papers, of which 4 invited, making imec the biggest contributing organization at the conference. The papers show progress in a variety of domains such as logic, memory, power device technology. More specifically, imec reports breakthroughs in monolithic GaN Power ICs, CMOS-compatible nano-scale domain wall devices, 3D SOC design, backside interconnects, IGZO-based DRAM cell architecture for (3D-)DRAM memories and novel 2D device architectures for large-scale quantum computers. Imec is also hosting a short course on the practical implementation of wireless power transfer, presented by Hubregt Visser.

Imec highlights

200 V GaN-on-SOI Smart Power Platform for Monolithic GaN Power ICs, T. Cosnier et al.

Abstract: This paper demonstrates a 200 V GaN-on-SOI smart power ICs platform developed on 200 mm substrates. Depletion-mode (d-mode) MIS-HEMTs and Gated-Edge-Termination Schottky barrier diodes (GET-SBDs) have been successfully integrated in an enhancement-mode (e-mode) HEMT technology baseline. A variety of low-voltage devices and passive components further supports the GaN ICs platform.

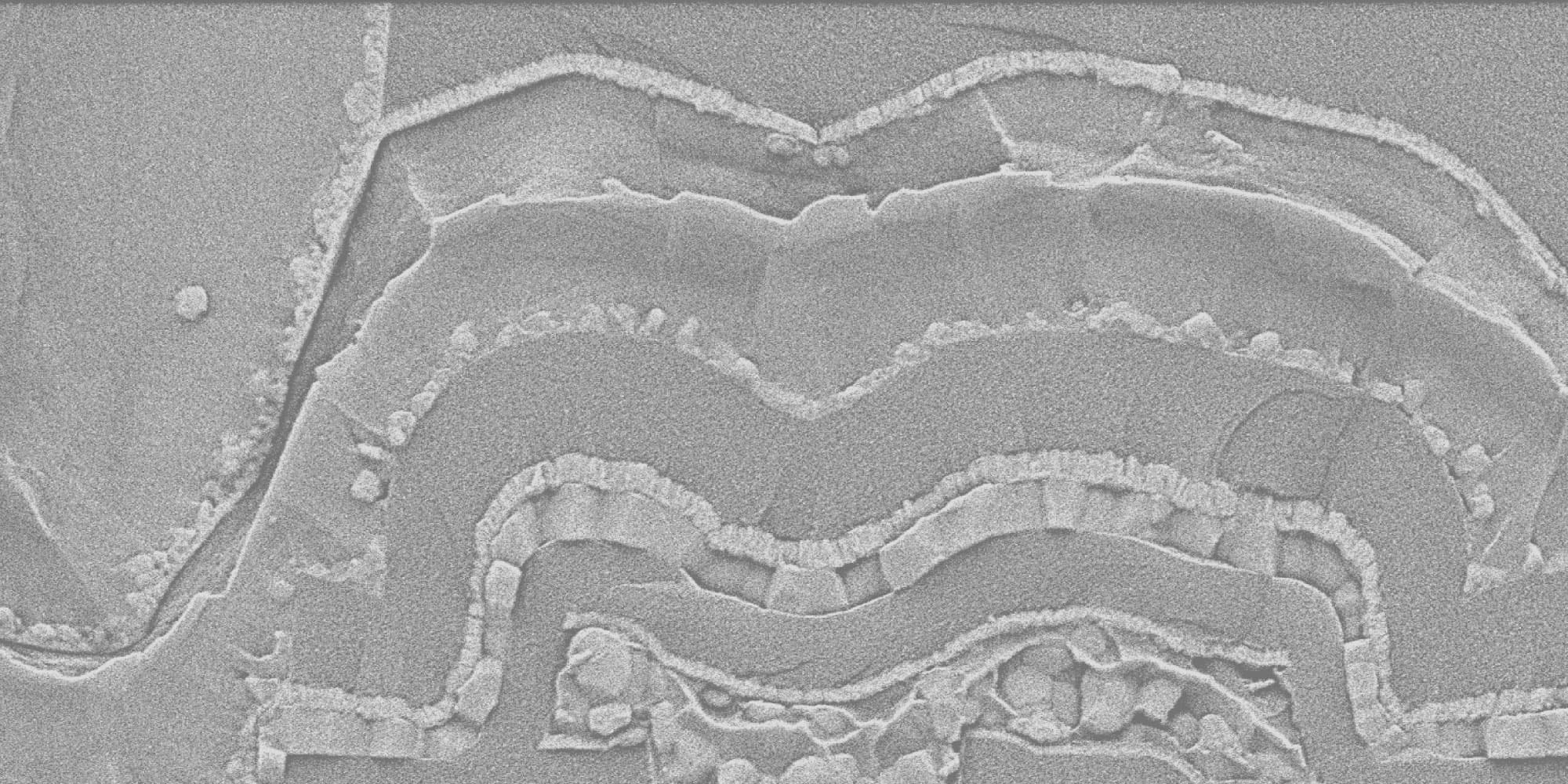

Magnetic domain walls: from physics to devices (invited), E. Raymenants, et al.

Abstract: Domain wall (DW) motion offers a flexible design for novel computational schemes. This paper provides an overview of DW physics and its applications. Experimentally, we demonstrate a full electrical operation of nanoscale DW devices, fabricated on 300 mm wafer. Finally, the prospective of device geometries for logic functionalities is discussed.

SoC integration, beyond 2.5D chiplets (Invited), E. Beyne, et al.

Abstract: 2.5D “Chiplet” integration is mainly limited to latency-tolerant applications. In contrast, the “3D-SoC” design approach, an extension of the 2D System-on-Chip design methodology, reduces latency between block. In 3D-SoC, the system is automatically partitioned into separate chips that are concurrently designed & interconnected in the 3rd dimension with scaled pitches.

Design and Optimization of SRAM Macro and Logic Using Backside Interconnects at 2nm node, R. Chen, et al.

Abstract: We explore the resource of backside (BS) interconnect for signal routing in SRAM macro and logic at 2nm technology node to tackle the technology scaling induced frontside (FS) BEOL routing congestion challenge. Compared to the FS BEOL, the BS routing is very beneficial in improving performance of long interconnect signals.

Tailoring IGZO-TFT architecture for capacitorless DRAM, demonstrating > 1E3s retention,>1E11 cycles endurance and Lg scalability down to 14nm, A. Belmonte, et al.

We demonstrate a fully 300-mm BEOL-compatible IGZO-based capacitorless DRAM cell with >1E3s retention and >1E11 endurance lifetime. We evaluate the impact of the IGZO-TFT architecture on the memory performance, and we achieve >100s retention down to Lg=14nm. We also prove capacitorless DRAM cell functionality with conformal IGZO deposition.

Understanding and modelling the PBTI reliability of thin-film IGZO transistors, A. Chasin, et al.

Abstract: The degradation process can be composed of up to four mechanisms with different kinetics, voltage acceleration factors and activation energies. Optimized devices achieve record lifetime of 1 year continuous operation at 95°C and Vov=1V.

Large-Scale 2D Spin-Based Quantum Processor with a Bi-Linear Architecture, F.A. Mohiyaddin, et al.

Abstract: We propose a bi-linear device architecture for silicon-based quantum processors. Using advanced modeling, we report critical dimensions, gate-times, fidelities, and on-chip resources for error correction. Our design is compact, realizable with existing fabrication technology, and allows planar integration of control circuitry, thereby providing a scalable route for silicon quantum computers.

Overview of imec contributions: papers and short courses

Sunday, December 12, 2021

Short Course 2: Emerging Technologies for Low Power Edge Computing

Practical implementation of wireless power transfer, Hubregt Visser

Monday, December 13, 2021

Session 3: Advanced Logic Technology Focus Session- Stacking of devices, circuits, chips: design, fabrication, metrology - challenges and opportunities

3-3 Inspection and metrology challenges for 3 nm node devices and beyond (Invited), T. Shohjoh, M. Ikota, M. Isawa, (Hitachi High-Tech Corporation ), G. F. Lorusso (imec), et al.

3-6 3D SoC integration, beyond 2.5D chiplets (Invited), E. Beyne, et al.

Session 5: Power Devices and Systems - GaN power devices, technologies, and circuits

5-1 200 V GaN-on-SOI Smart Power Platform for Monolithic GaN Power ICs, T. Cosnier et al.

7-4 Dual gate synthetic MoS2 MOSFETs with 4.56μF/cm2 channel capacitance, 320μS/ μm Gm and 420 μA/ μm Id at 1V Vd/100nm Lg, X. Wu et al.

8-4 Understanding the ISPP Slope in Charge Trap Flash Memory and its Impact on 3D NAND Scaling, D. Verreck, et al.

Tuesday, December 14

Session 10: Memory Technology - Charge-based Memories

10-2 Understanding the kinetics of Metal Induced Lateral Crystallization process to enhance the poly-Si channel quality and current conduction in 3-D NAND memory, S. Ramesh, et al.

10-6 Tailoring IGZO-TFT architecture for capacitorless DRAM, demonstrating > 1E3s retention,>1E11 cycles endurance and Lg scalability down to 14nm, A. Belmonte, et al.

Session 17: Memory Technology - Emerging Non-Volatile Memories

17-6 Demonstration of a Free-layer Developed With Atomistic Simulations Enabling BEOL Compatible VCMA-MRAM with a Coefficient ≥100fJ/Vm, R., et al.

Session 22: Advanced Logic Technology - Front- and back-side advanced interconnects

22-4 Design and Optimization of SRAM Macro and Logic Using Backside Interconnects at 2nm node, R. Chen, et al.

22-5 Buried Power Rail Metal exploration towards the 1 nm Node, A. Gupta, et al.

Wednesday, December 15

Session 25: Memory Technology/Modeling And Simulation/Advanced Logic Technology Focus Session - STCO for memory-centric computing and 3D integration

25-1 Human-centric Computing (Invited), J.M. Rabaey, University of California at Berkeley and imec

Session 26: Advanced Logic Technology - Advances in Nanosheet FET devices

26-2 Comparison of Electrical Performance of Co-Integrated Forksheets and Nanosheets Transistors for the *nm Technological Node and Beyond, R. Ritzenthaler, et al.

Session 27: Modeling and Simulation - Low-dimensional and spin-based devices

27-5 Large-Scale 2D Spin-Based Quantum Processor with a Bi-Linear Architecture, F. A. Mohiyaddin,et al.

Session 28: Memory Technology - Memory Technology - Emerging memory (PCRAM/OTS)

28-4 Polarity-dependent threshold voltage shift in ovonic threshold switches: Challenges and opportunities, T. Ravsher (KU Leuven), R. Degraeve (imec), et al.

Session 31: Reliability of Systems and Devices - Advanced Logic Device Reliability

31-1 Understanding and modelling the PBTI reliability of thin-film IGZO transistors, A. Chasin, et al.

Session 32: Emerging Device and Compute Technology - CMOS+X Devices: New Microwave, Millimeter Wave and Analogerials and Spintronics

31-4 Low-temperature atomic and molecular hydrogen anneals for enhanced chemical SiO2 ILquality in low thermal budget RMG stacks, J. Franco, et al.

32-3 Magnetic domain walls: from physics to devices (Invited), E. Raymenants, et al.

34-2 Scaling of double-gated WS2 FETs to sub-5nm physical gate length fabricated in a 300mm FAB, Q. Smets, et al.

37-1 Superior electrostatic control in uniform monolayer MoS2 scaled transistors via in-situ surface smoothening, Y. Shi, et al.

39-5 ESD HBM Discharge Model in RF GaN-on-Si (MIS)HEMTs, W.-M. Wu, et al.

40-5 High-Performance 300mm Integrated Superconducting Resonators for Quantum Computing Applications, M. Mongillo, et al.

More information see 2021 IEEE IEDM – Program Overview